## 8253/8253-5 PROGRAMMABLE INTERVAL TIMER

- MCS-85<sup>TM</sup> Compatible 8253-5

- 3 Independent 16-Bit Counters

- DC to 2.6 MHz

- Programmable Counter Modes

- Count Binary or BCD

- Single + 5V Supply

- Available in EXPRESS

- Standard Temperature Range

- Extended Temperature Range

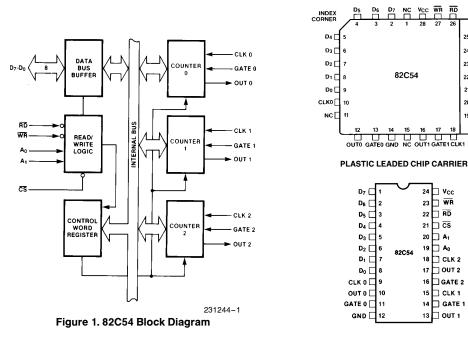

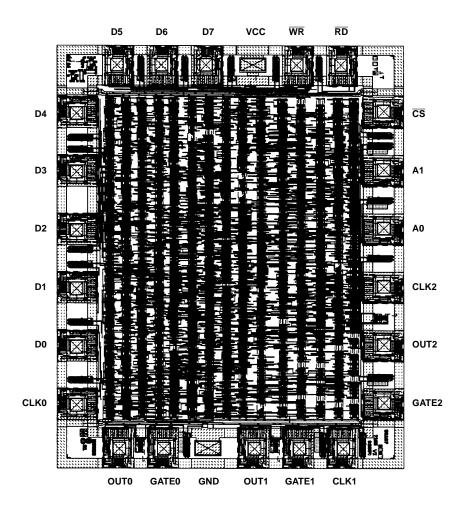

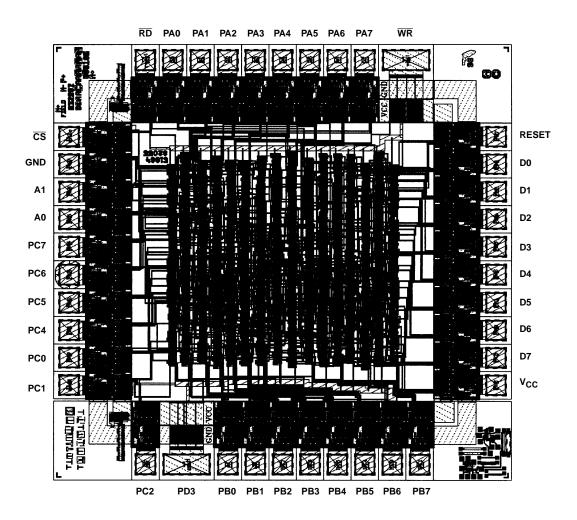

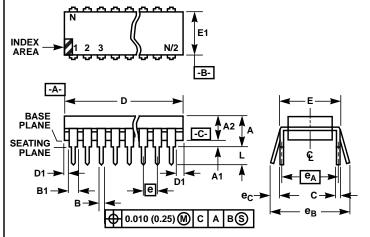

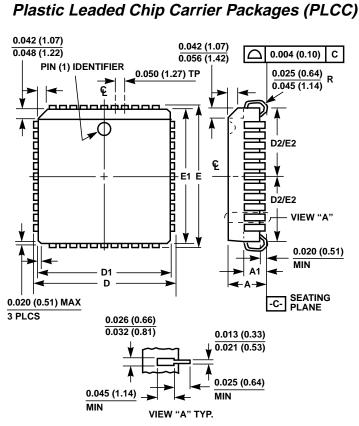

The Intel® 8253 is a programmable counter/timer device designed for use as an Intel microcomputer peripheral. It uses NMOS technology with a single +5V supply and is packaged in a 24-pin plastic DIP.

It is organized as 3 independent 16-bit counters, each with a count rate of up to 2.6 MHz. All modes of operation are software programmable.

1.1.3

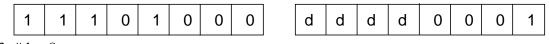

| ĈŜ  | RD  | WR                    | A <sub>1</sub> | A <sub>0</sub> |                      |

|-----|-----|-----------------------|----------------|----------------|----------------------|

| 0   | 1   | 0                     | 0              | 0 ·            | Load Counter No. 0   |

| 0   | 1   | 0                     | 0              | 1              | Load Counter No. 1   |

| 0   | 1   | 0                     | 1              | 0              | Load Counter No. 2   |

| . 0 | 1   | 0                     | 1              | 1              | Write Mode Word      |

| 0   | 0   | 1                     | 0              | 0              | Read Counter No. 0   |

| 0   | 0   | 1                     | 0              | 1              | Read Counter No. 1   |

| 0   | 0   | 1                     | 1              | 0              | Read Counter No. 2   |

| 0   | - 0 | 1                     | 1              | 1              | No-Operation 3-State |

| 1   | X   | <b>X</b> <sup>*</sup> | X              | X              | Disable 3-State      |

| 0   | 1   | 1                     | X              | X              | No-Operation 3-State |

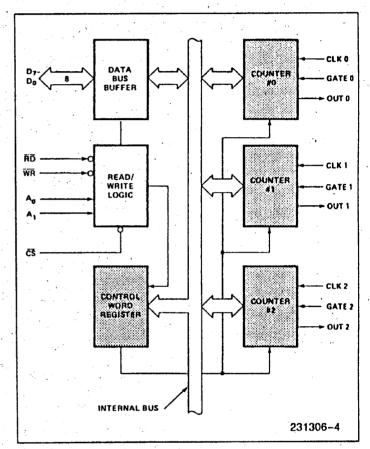

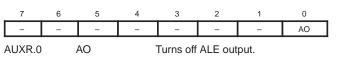

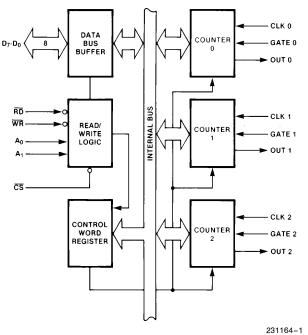

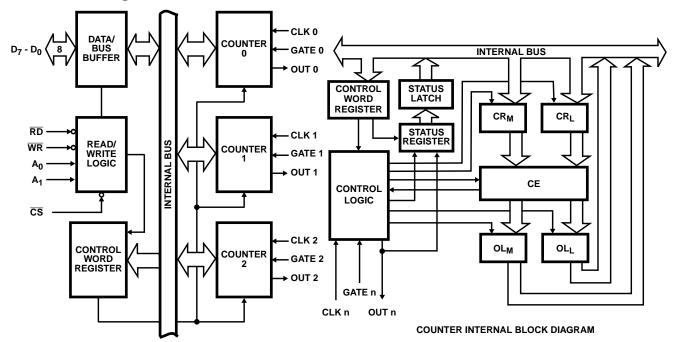

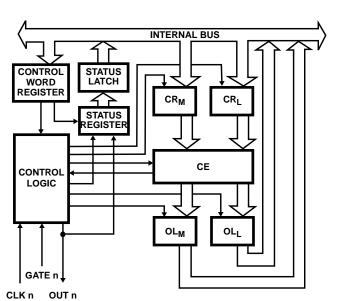

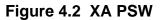

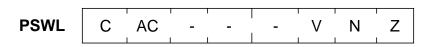

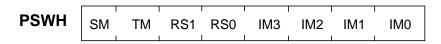

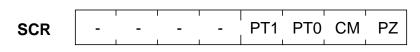

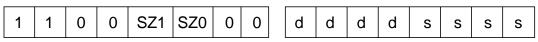

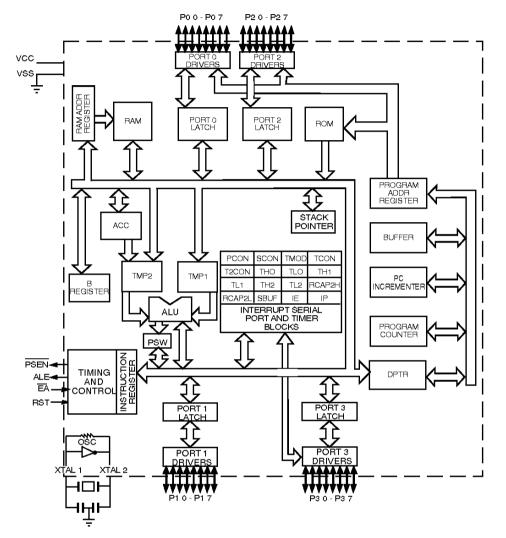

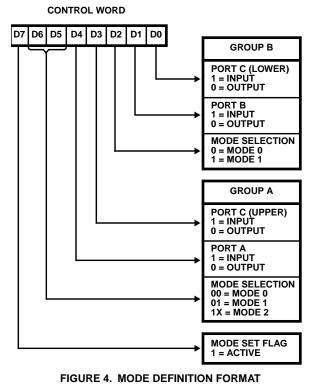

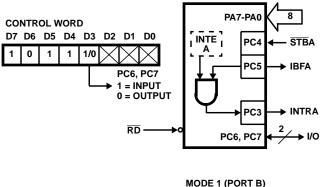

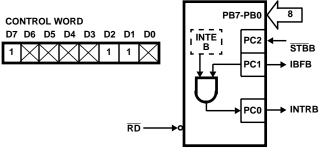

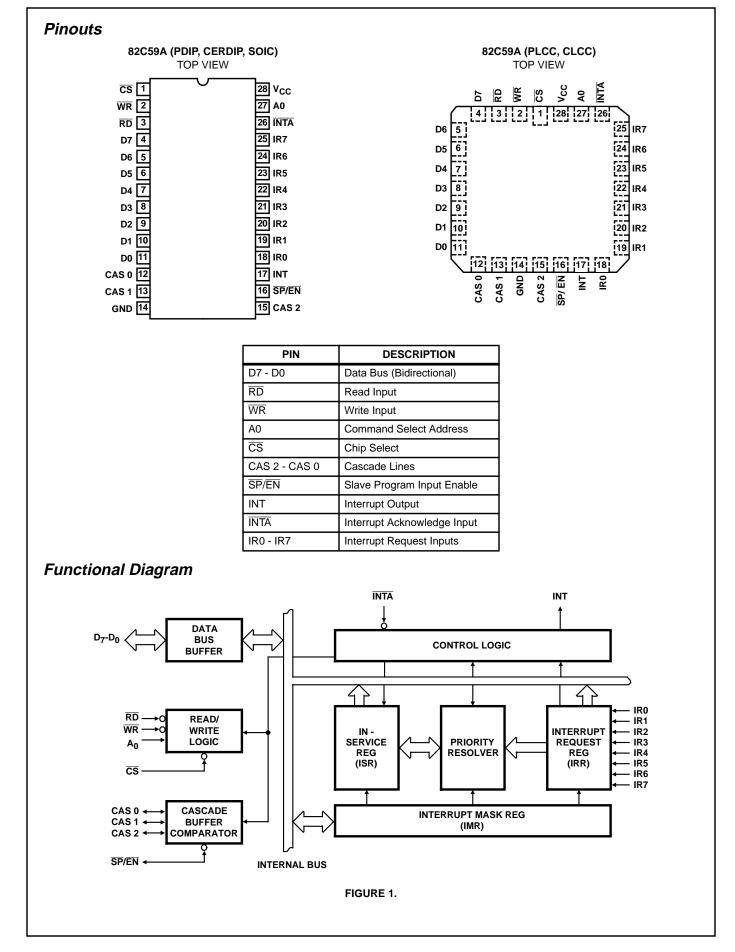

### **Control Word Register**

The Control Word Register is selected when A0, A1 are 11. It then accepts information from the data bus buffer and stores it in a register. The information stored in this register controls the operation MODE of each counter, selection of binary or BCD counting and the loading of each count register.

The Control Word Register can only be written into; no read operation of its contents is available.

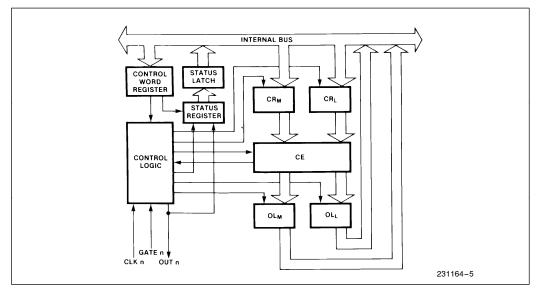

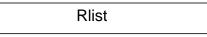

### Counter #0, Counter #1, Counter #2

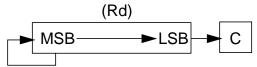

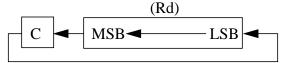

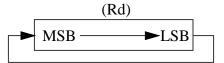

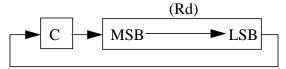

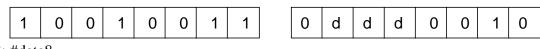

These three functional blocks are identical in operation so only a single counter will be described. Each Counter consists of a single, 16-bit, pre-settable, DOWN counter. The counter can operate in either binary or BCD and its input, gate and output are configured by the selection of MODES stored in the Control Word Register.

The counters are fully independent and each can have separate MODE configuration and counting operation, binary or BCD. Also, there are special features in the control word that handle the loading of the count value so that software overhead can be minimized for these functions.

The reading of the contents of each counter is available to the programmer with simple READ operations for event counting applications and special commands and logic are included in the 8253 so that the contents of each counter can be read "on the fly" without having to inhibit the clock input.

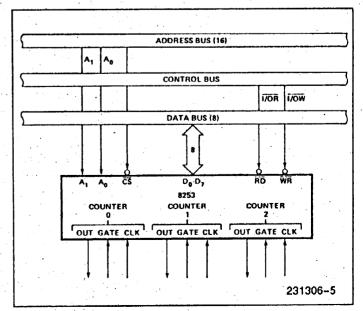

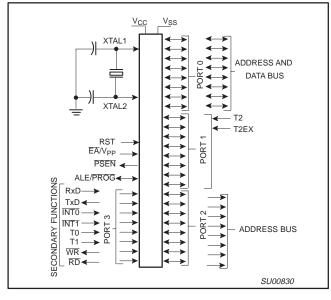

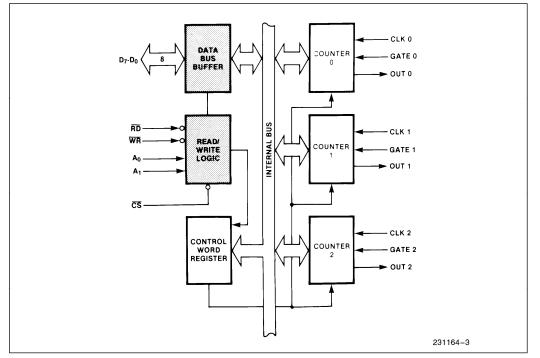

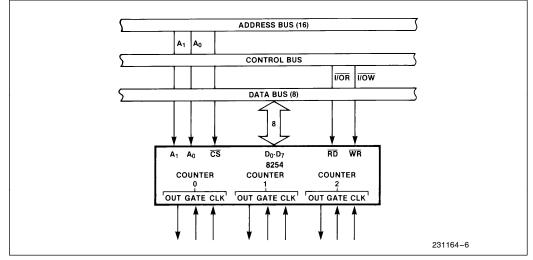

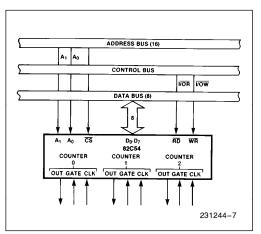

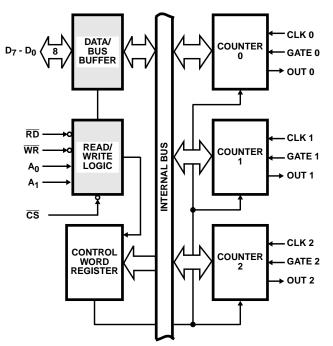

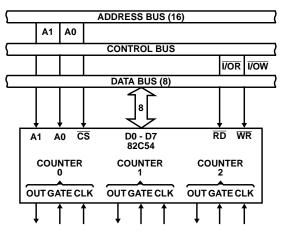

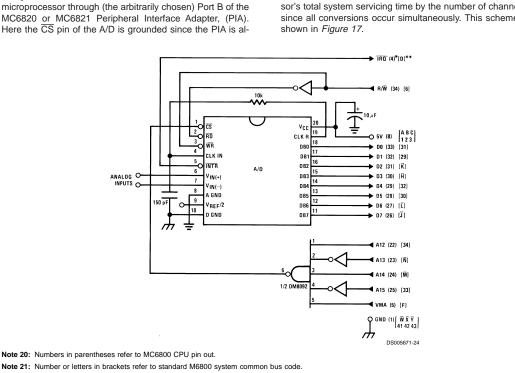

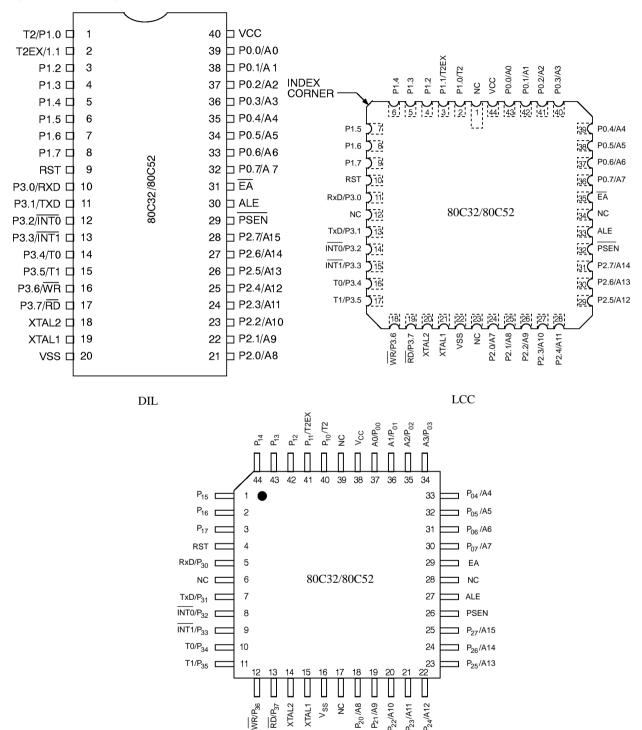

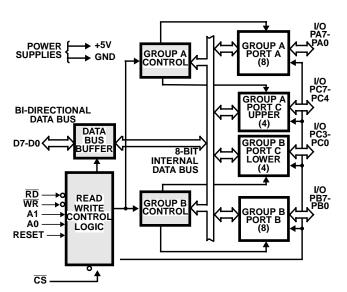

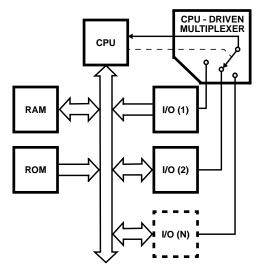

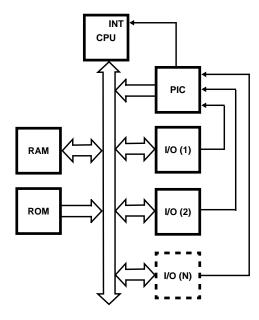

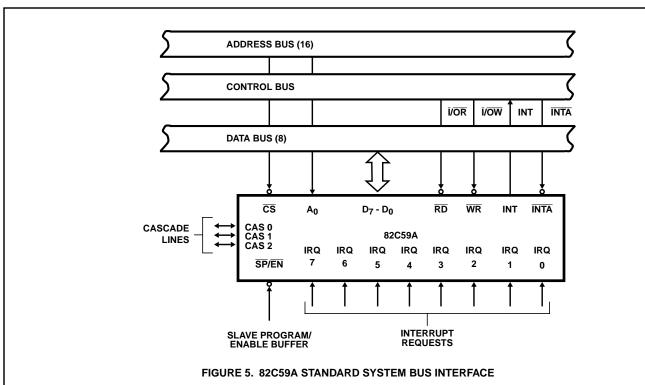

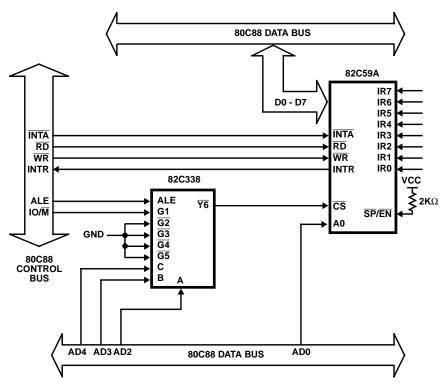

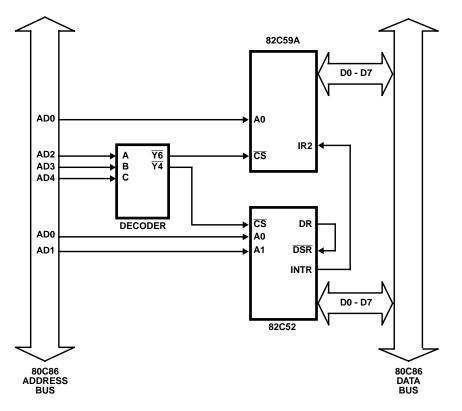

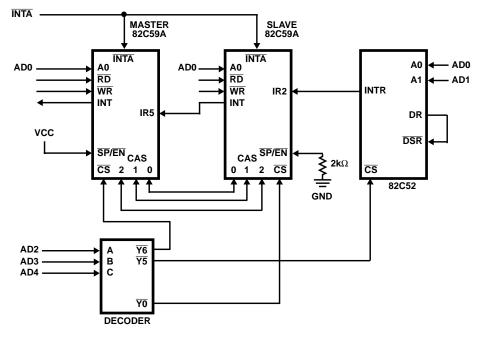

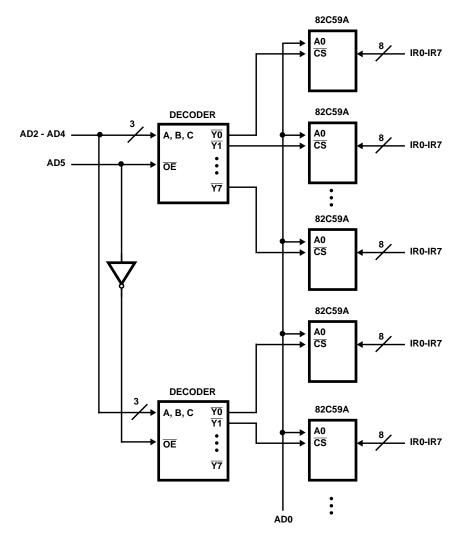

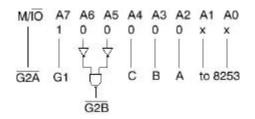

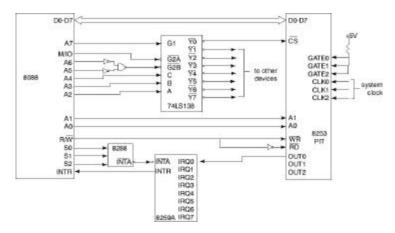

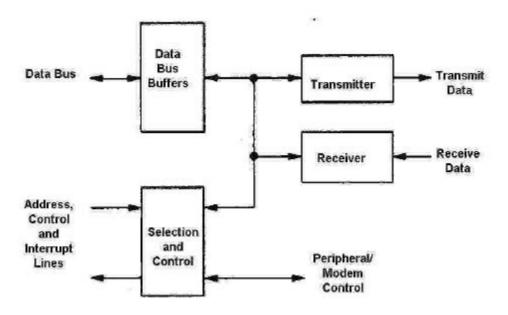

### 8253 SYSTEM INTERFACE

The 8253 is a component of the Intel<sup>™</sup> Microcomputer systems and interfaces in the same manner as all other peripherals of the family. It is treated by the

systems software as an array of peripheral I/O ports; three are counters and the fourth is a control register for MODE programming.

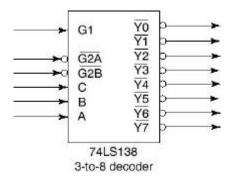

Basically, the select inputs A0, A1 connect to the A0, A1 address bus signals of the CPU. The  $\overline{CS}$  can be derived directly from the address bus using a linear select method. Or it can be connected to the output of a decoder, such as an Intel 8205 for larger systems.

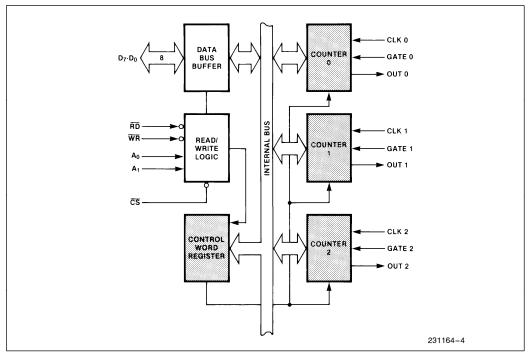

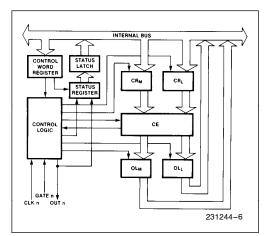

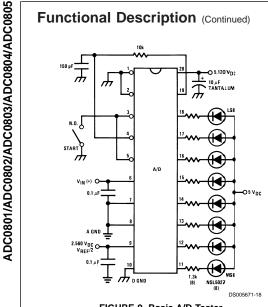

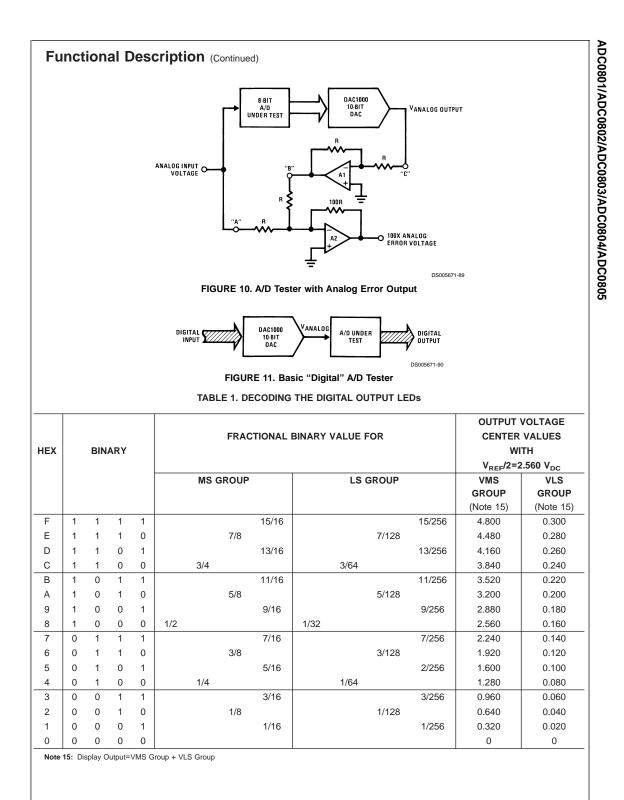

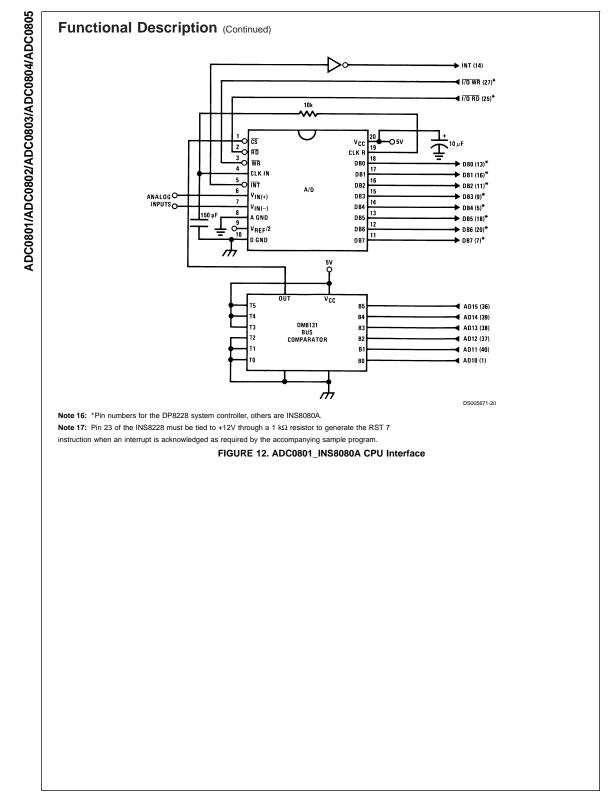

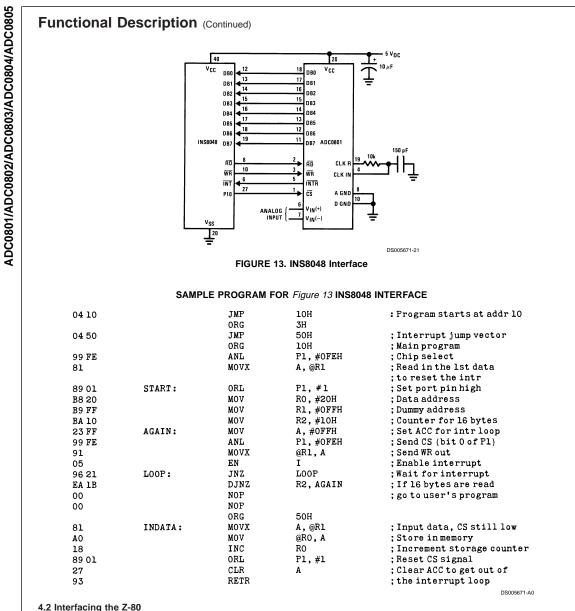

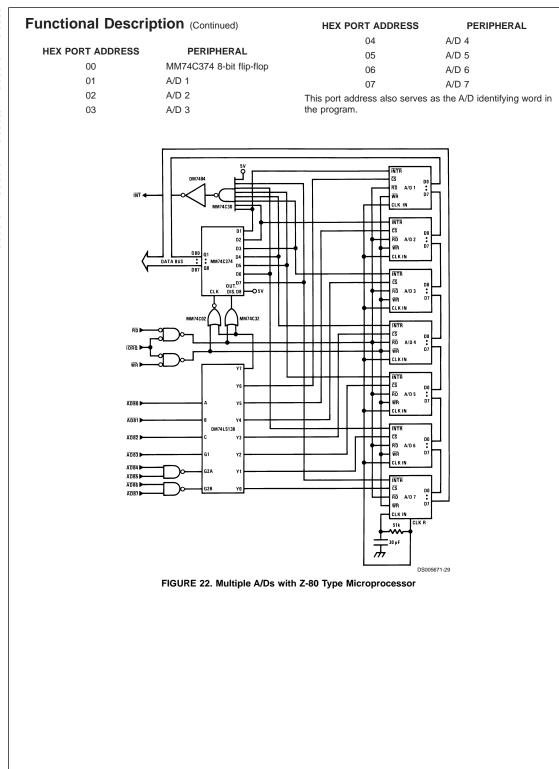

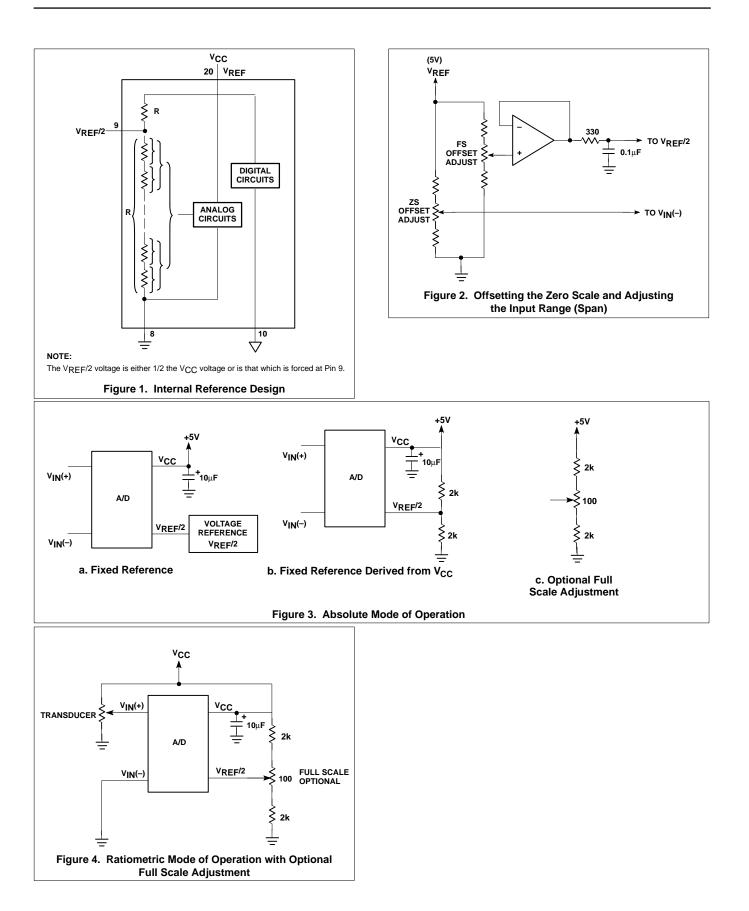

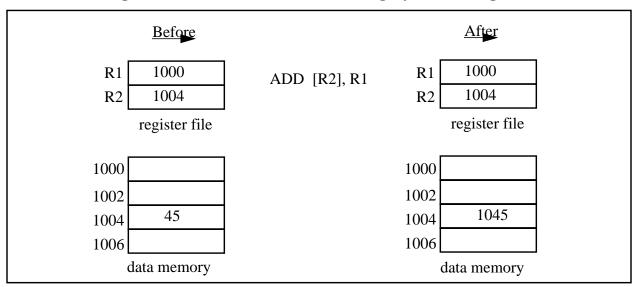

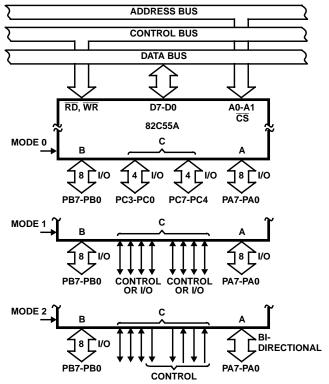

Figure 4. Block Diagram Showing Control Word Register and Counter Functions

Figure 5. 8253 System Interface

### **OPERATIONAL DESCRIPTION**

### General

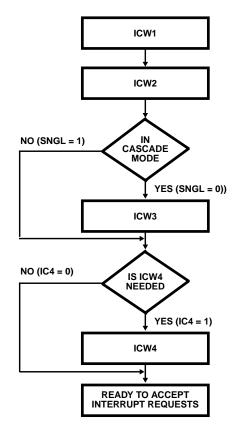

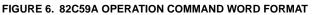

The complete functional definition of the 8253 is programmed by the systems software. A set of control words *must* be sent out by the CPU to initialize each counter of the 8253 with the desired MODE and quantity information. Prior to initialization, the MODE, count, and output of all counters is undefined. These control words program the MODE, Loading sequence and selection of binary or BCD counting.

Once programmed, the 8253 is ready to perform whatever timing tasks it is assigned to accomplish.

The actual counting operation of each counter is completely independent and additional logic is provided on-chip so that the usual problems associated with efficient monitoring and management of external, asynchronous events or rates to the microcomputer system have been eliminated.

### Programming the 8253

All of the MODES for each counter are programmed by the systems software by simple I/O operations.

Each counter of the 8253 is individually programmed by writing a control word into the Control Word Register. (A0, A1 = 11)

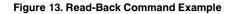

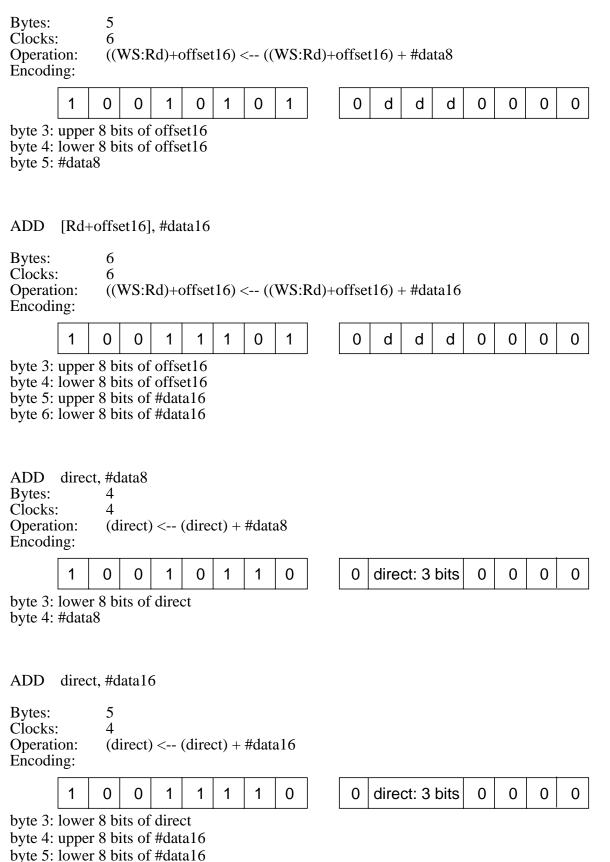

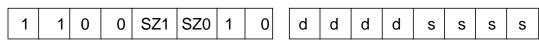

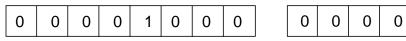

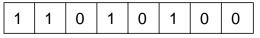

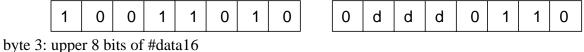

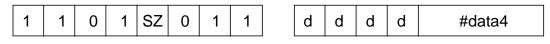

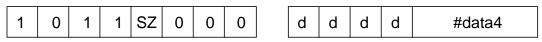

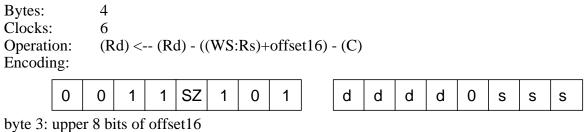

## **Control Word Format**

| D7  | D <sub>6</sub> | D5  | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub> | D <sub>0</sub> |

|-----|----------------|-----|----------------|----------------|----------------|----------------|----------------|

| SC1 | SC0            | RL1 | RL0            | M2             | M1             | М0             | BCD            |

### **Definition Of Control**

### SC-SELECT COUNTER:

| SC1 | SC0 |                  |

|-----|-----|------------------|

| 0   | 0   | Select Counter 0 |

| 0.  | 1   | Select Counter 1 |

| . 1 | 0   | Select Counter 2 |

| 1   | 1   | Illegal          |

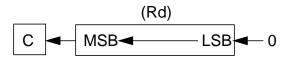

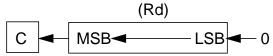

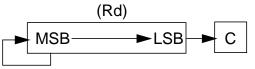

### RL-READ/LOAD:

### RL1 RL0

| .0 | 0 | Counter Latching operation (see READ/WRITE Procedure Section).      |

|----|---|---------------------------------------------------------------------|

| 1  | 0 | Read/Load most significant byte only.                               |

| 0  | 1 | Read/Load least significant byte only.                              |

| 1  | 1 | Read/Load least significant byte first, then most significant byte. |

### M-MODE:

| M2 | M1  | MO       | •       |

|----|-----|----------|---------|

| 0  | 0   | 0        | Mode 0. |

| 0  | 0   | 1 · · ·  | Mode 1  |

| Х  | 1   | 0        | Mode 2  |

| X  | • 1 | <b>1</b> | Mode 3  |

| 1  | 0   | 0        | Mode 4  |

| 1  | 0   | . 1      | Mode 5  |

### BCD:

| 0 | Binary Counter 16-Bits             |

|---|------------------------------------|

| 1 | Binary Coded Decimal (BCD) Counter |

|   | (4 Decades)                        |

### **Counter Loading**

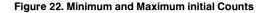

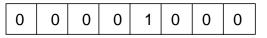

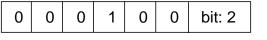

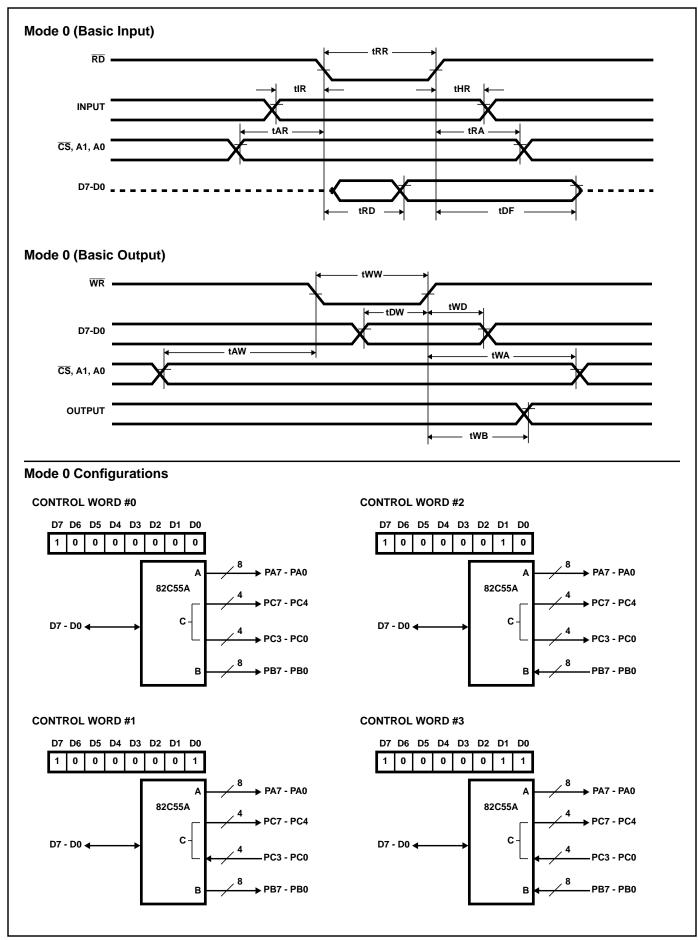

The count register is not loaded until the count value is written (one or two bytes, depending on the mode selected by the RL bits), followed by a rising edge and a falling edge of the clock. Any read of the counter prior to that falling clock edge may yield invalid data.

### MODE DEFINITION

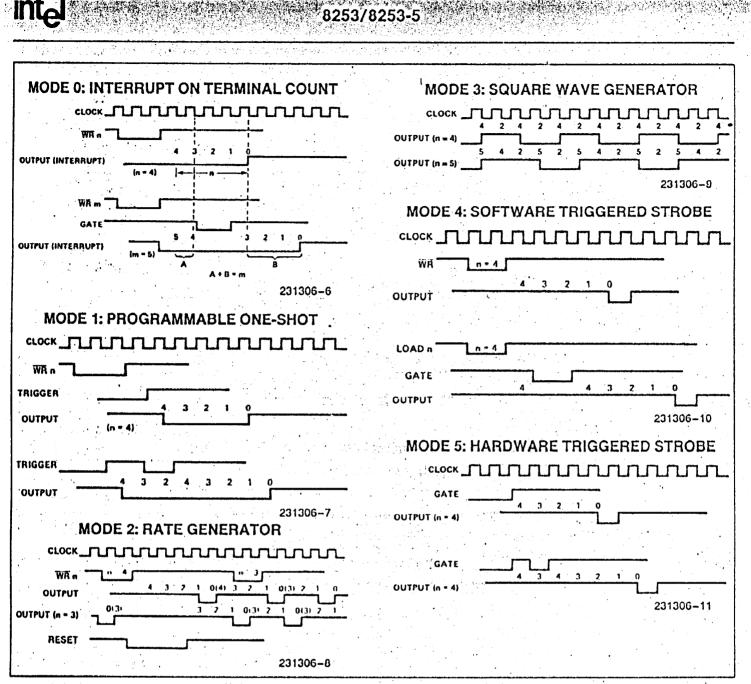

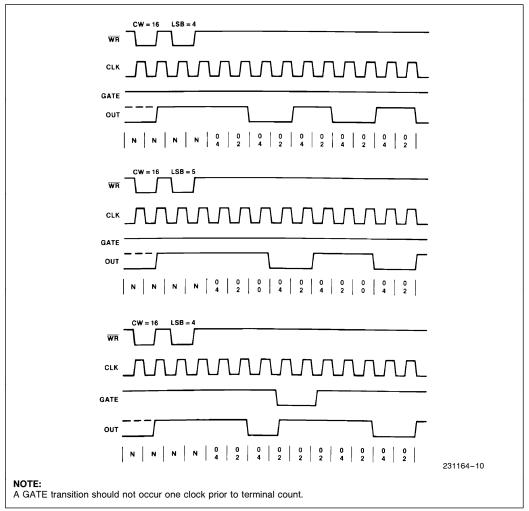

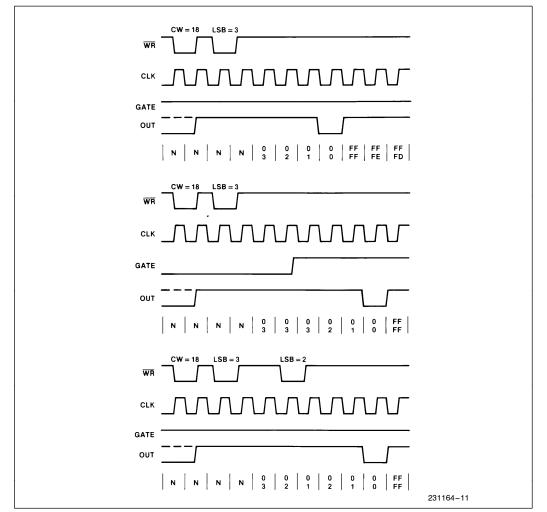

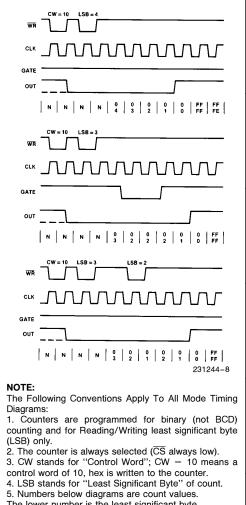

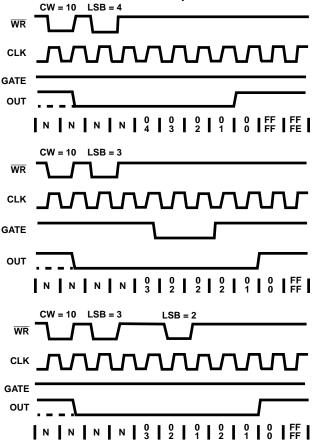

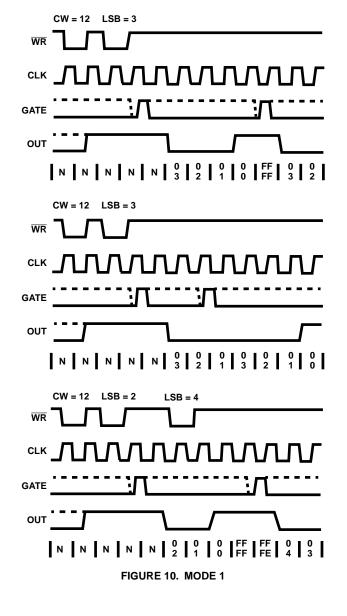

**MODE 0: Interrupt on Terminal Count.** The output will be initially low after the mode set operation. After the count is loaded into the selected count register, the output will remain low and the counter will count. When terminal count is reached, the output will go high and remain high until the selected count register is reloaded with the mode or a new count is loaded. The counter continues to decrement after terminal count has been reached.

Rewriting a counter register during counting results in the following:

- (1) Write 1st byte stops the current counting.

- (2) Write 2nd byte starts the new count.

- 2-17

# intel

### 8253/8253-5

### FUNCTIONAL DESCRIPTION

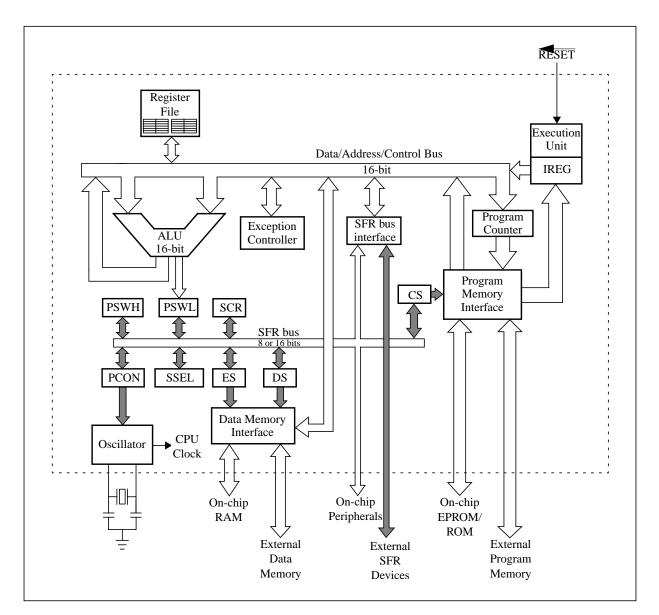

### General

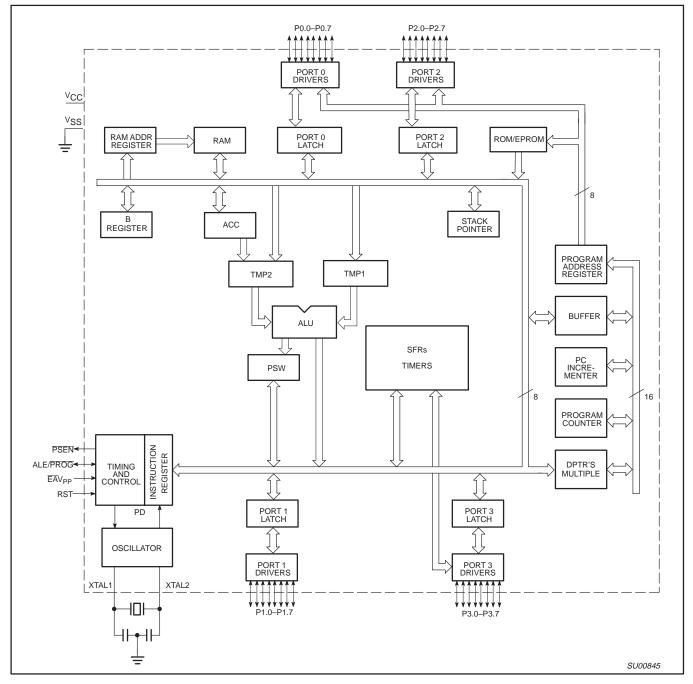

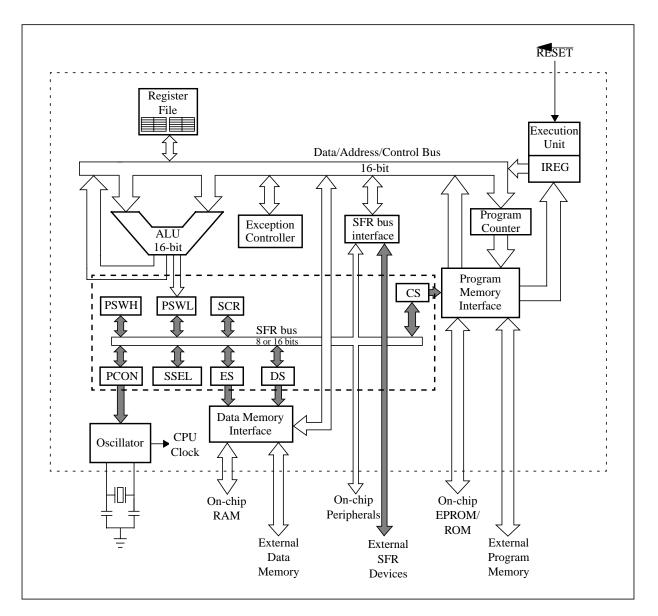

The 8253 is programmable interval timer/counter specifically designed for use with the Intel<sup>TM</sup> Microcomputer systems. Its function is that of a general purpose, multi-timing element that can be treated as an array of I/O ports in the system software.

The 8253 solves one of the most common problems in any microcomputer system, the generation of accurate time delays under software control. Instead of setting up timing loops in systems software, the programmer configures the 8253 to match his requirements, initializes one of the counters of the 8253 with the desired quantity, then upon command the 8253 will count out the delay and interrupt the CPU when it has completed its tasks. It is easy to see that the software overhead is minimal and that multiple delays can easily be maintained by assignment of priority levels.

Other counter/timer functions that are non-delay in nature but also common to most microcomputers can be implemented with the 8253.

- Programmable Rate Generator

- Event Counter

- Binary Rate Multiplier

- Real Time Clock

- Digital One-Shot

- Complex Motor Controller

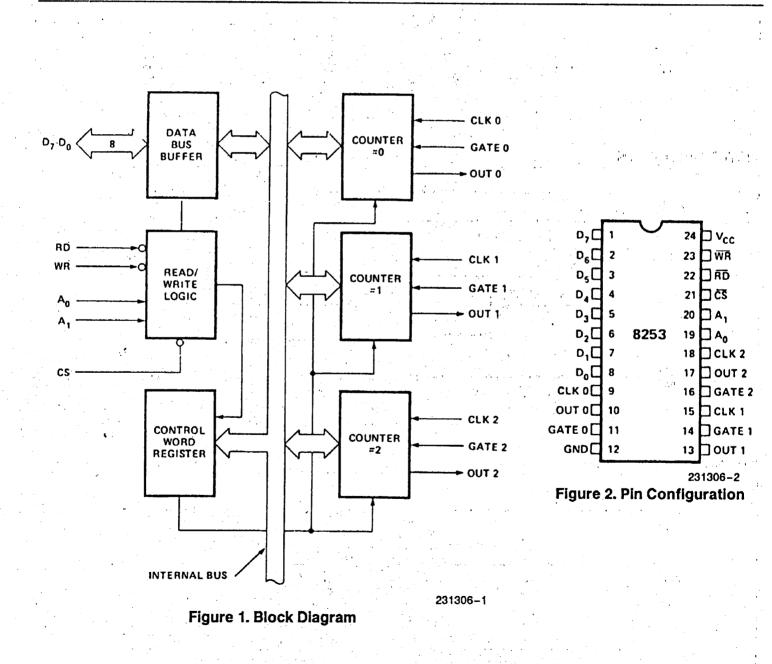

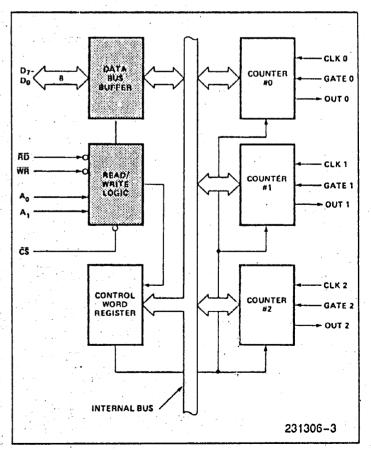

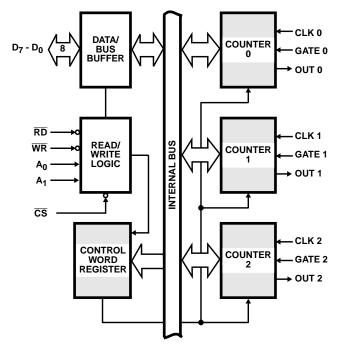

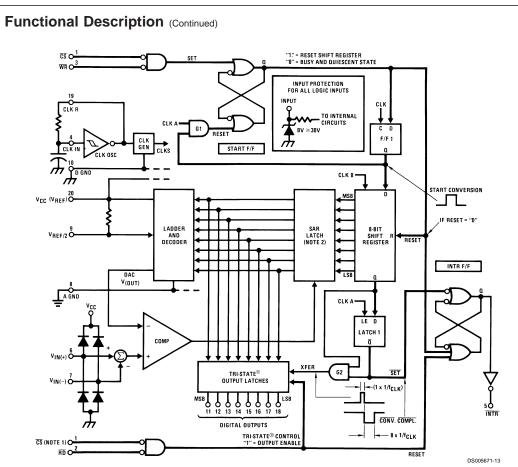

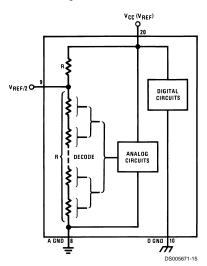

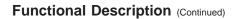

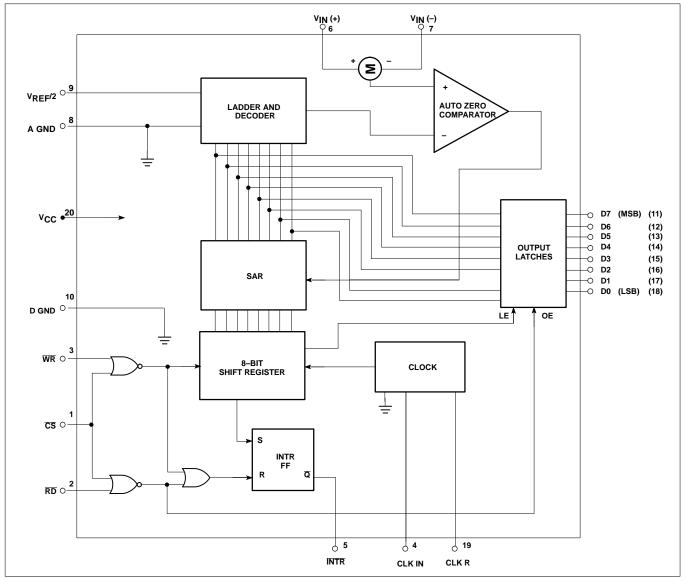

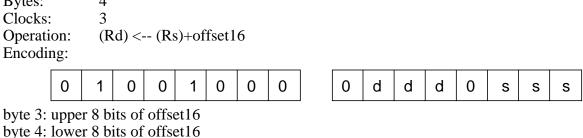

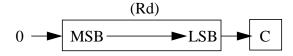

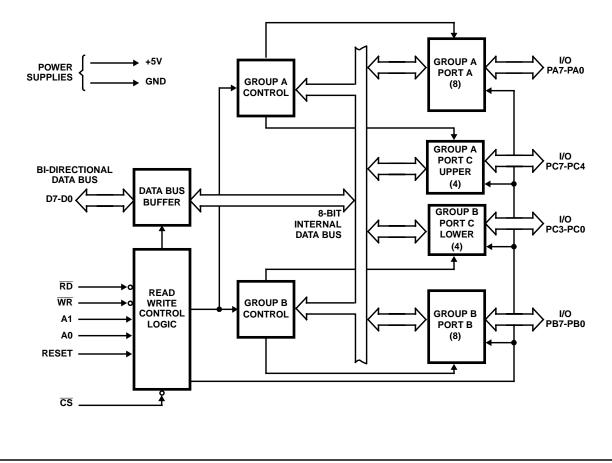

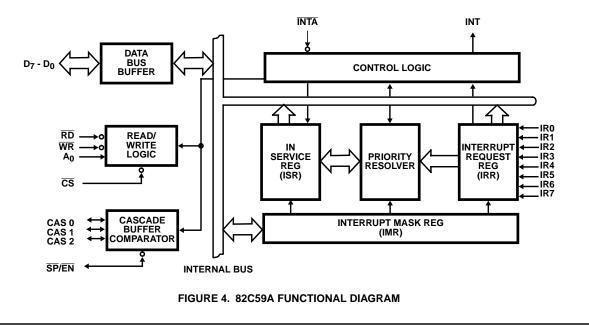

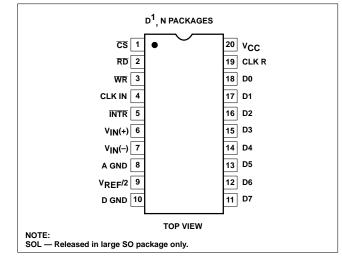

### **Data Bus Buffer**

The 3-state, bi-directional, 8-bit buffer is used to interface the 8253 to the system data bus. Data is transmitted or received by the buffer upon execution of INput or OUTput CPU instructions. The Data Bus Buffer has three basic functions.

- 1. Programming the MODES of the 8253.

- 2. Loading the count registers.

- 3. Reading the count values.

### **Read/Write Logic**

The Read/Write Logic accepts inputs from the system bus and in turn generates control signals for overall device operation. It is enabled or disabled by CS so that no operation can occur to change the function unless the device has been selected by the system logic.

## **RD** (Read)

A "low" on this input informs the 8253 that the CPU is inputting data in the form of a counters value.

### WR (Write)

A "low" on this input informs the 8253 that the CPU is outputting data in the form of mode information or loading counters.

## A0, A1

These inputs are normally connected to the address bus. Their function is to select one of the three counters to be operated on and to address the control word register for mode selection.

## **CS** (Chip Select)

A "low" on this input enables the 8253. No reading or writing will occur unless the device is selected. The  $\overline{CS}$  input has no effect upon the actual operation of the counters.

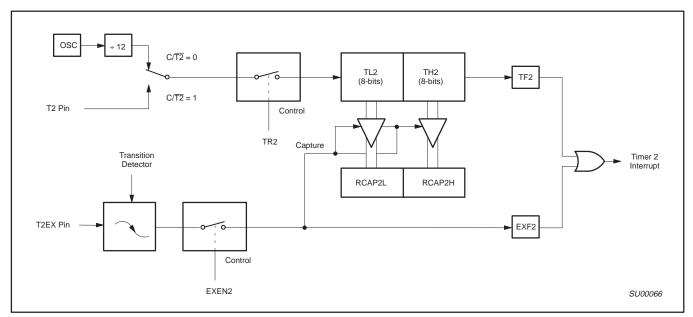

Figure 3. Block Diagram Showing Data Bus Buffer and Read/Write Logic Functions **MODE 1: Programmable One-Shot.** The output will go low on the count following the rising edge of the gate input.

The output will go high on the terminal count. If a new count value is loaded while the output is low it will not affect the duration of the one-shot pulse until the succeeding trigger. The current count can be read at any time without affecting the one-shot pulse.

The one-shot is retriggerable, hence the output will remain low for the full count after any rising edge of the gate input.

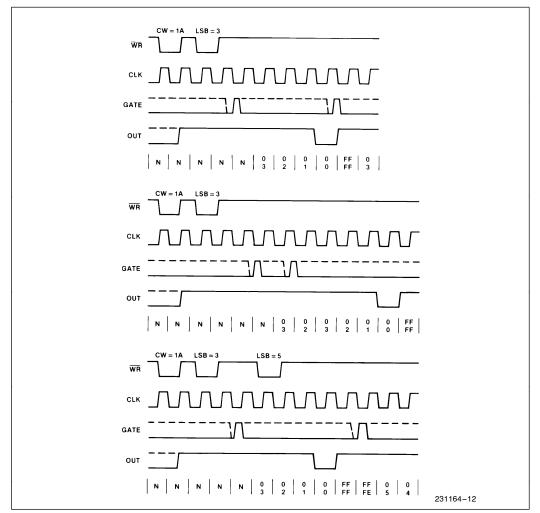

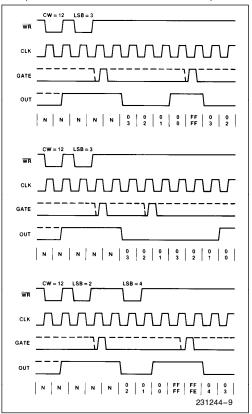

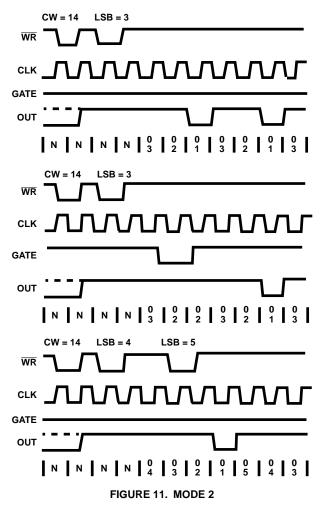

**MODE 2: Rate Generator.** Divide by N counter. The output will be low for one period of the input clock. The period from one output pulse to the next equals the number of input counts in the count register. If the count register is reloaded between output pulses the present period will not be affected, but the subsequent period will reflect the new value.

The gate input, when low, will force the output high. When the gate input goes high, the counter will start from the initial count. Thus, the gate input can be used to synchronize the counter.

When this mode is set, the output will remain high until after the count register is loaded. The output then can also be synchronized by software.

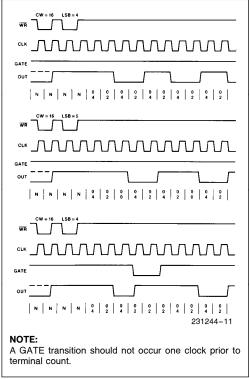

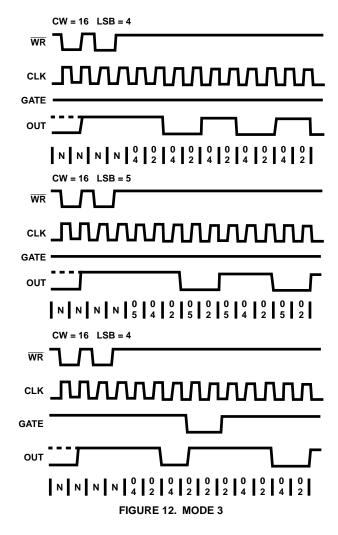

MODE 3: Square Wave Rate Generator. Similar to MODE 2 except that the output will remain high until one half the count has been completed (or even numbers) and go low for the other half of the count. This is accomplished by decrementing the counter by two on the falling edge of each clock pulse. When the counter reaches terminal count, the state of the output is changed and the counter is reloaded with the full count and the whole process is repeated.

If the count is odd and the output is high, the first clock pulse (after the count is loaded) decrements the count by 1. Subsequent clock pulses decrement the clock by 2. After timeout, the output goes low and the full count is reloaded. The first clock pulse (following the reload) decrements the counter by 3. Subsequent clock pulses decrement the count by 2 until timeout. Then the whole process is repeated. In this way, if the count is odd, the output will be high for (N + 1)/2 counts and low for (N - 1)/2 counts.

In Modes 2 and 3, if a CLK source other than the system clock is used, GATE should be pulsed immediately following  $\overline{WR}$  of a new count value.

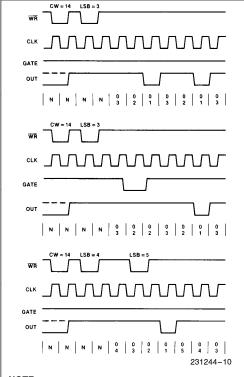

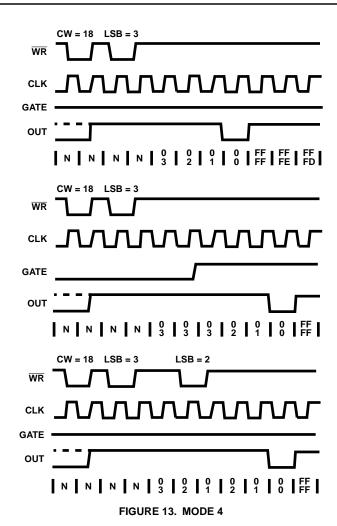

**MODE 4: Software Triggered Strobe.** After the mode is set, the output will be high. When the count is loaded, the counter will begin counting. On terminal count, the output will go low for one input clock period, then will go high again.

If the count register is reloaded during counting, the new count will be loaded on the next CLK pulse. The count will be inhibited while the GATE input is low.

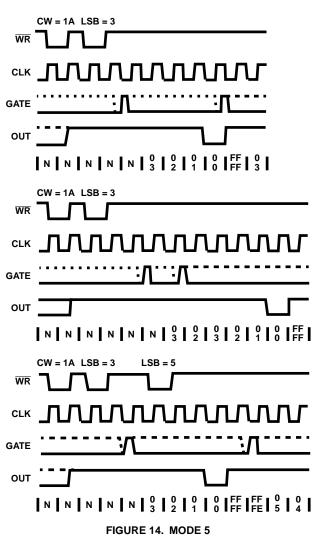

**MODE 5: Hardware Triggered Strobe.** The counter will start counting after the rising edge of the trigger input and will go low for one clock period when the terminal count is reached. The counter is retriggerable. The output will not go low until the full count after the rising edge of any trigger.

| Signa<br>Status<br>Modes | Or Going                                                                                | Rising                                                                                                                              | High                |

|--------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 0                        | Disables<br>counting                                                                    |                                                                                                                                     | Enables counting    |

| 1                        |                                                                                         | <ol> <li>1) Initiates         <ul> <li>counting</li> <li>2) Resets output</li> <li>after next</li> <li>clock</li> </ul> </li> </ol> | -                   |

| 2                        | <ol> <li>Disables<br/>counting</li> <li>Sets output<br/>immediately<br/>high</li> </ol> | 1) Reloads<br>counter<br>2) Initiates<br>counting                                                                                   | Enables<br>counting |

| 3                        | <ol> <li>Disables<br/>counting</li> <li>Sets output<br/>immediately<br/>high</li> </ol> | <ol> <li>1) Reloads<br/>counter</li> <li>2) Initiates<br/>counting</li> </ol>                                                       | Enables<br>counting |

| 4                        | Disables<br>counting                                                                    |                                                                                                                                     | Enables counting    |

| 5                        |                                                                                         | Initiates<br>counting                                                                                                               | -                   |

Figure 6. Gate Pin Operations Summary

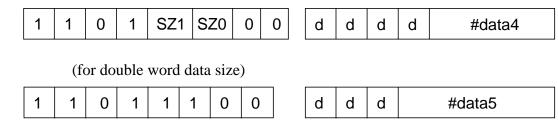

## 8253 READ/WRITE PROCEDURE

### Write Operations

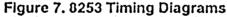

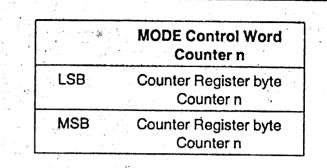

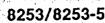

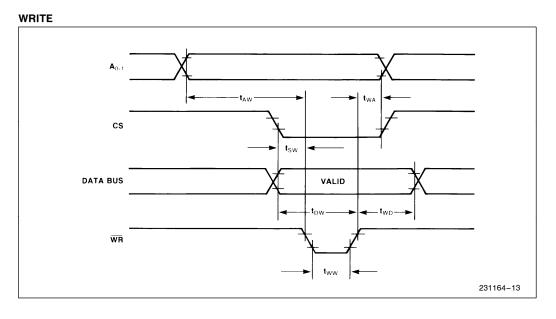

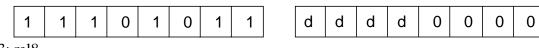

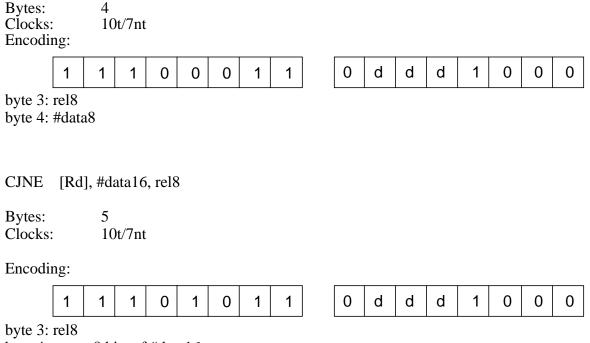

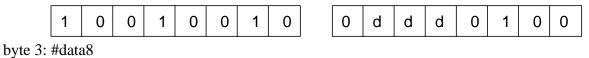

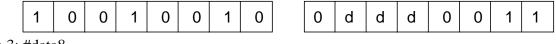

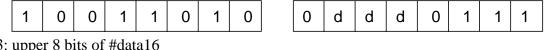

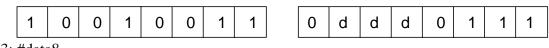

The systems software must program each counter of the 8253 with the mode and quantity desired. The programmer must write out to the 8253 a MODE control word and the programmed number of count register bytes (1 or 2) prior to actually using the selected counter.

The actual order of the programming is quite flexible. Writing out of the MODE control word can be in any sequence of counter selection, e.g., counter #0 does not have to be first or counter #2 last. Each counter's MODE control word register has a separate address so that its loading is completely sequence independent. (SC0, SC1).

The loading of the Count Register with the actual count value, however, must be done in exactly the sequence programmed in the MODE control word (RL0, RL1). This loading of the counter's count register is still sequence independent like the MODE control word loading, but when a selected count register is to be loaded it *must* be loaded with the number of bytes programmed in the MODE control word (RL0, RL1). The one or two bytes to be loaded in the count register do not have to follow the associated MODE control word. They can be programmed at any time following the MODE control word loading as long as the correct number of bytes is loaded in order.

All counters are down counters. Thus, the value loaded into the count register will actually be decremented. Loading all zeros into a count register will result in the maximum count (2<sup>16</sup> for Binary or 10<sup>4</sup> for BCD). In MODE 0 the new count will not restart until the load has been completed. It will accept one of two bytes depending on how the MODE control words (RL0, RL1) are programmed. Then proceed with the restart operation.

### NOTE:

Format shown is a simple example of loading the 8253 and does not imply that it is the only format that can be used.

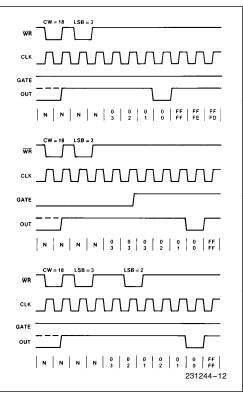

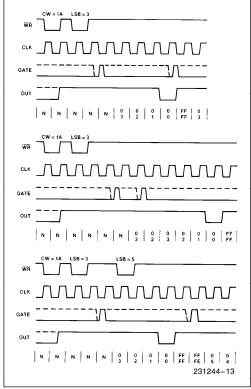

Figure 8. Programming Format

#### **A1 A0** MODE Control Word No. 1 1 1 Counter 0 MODE Control Word No. 2 1 1 Counter 1 **MODE Control Word** No. 3 1 1 Counter 2 **Count Register Byte** LSB No. 4 0 1 Counter 1 **Count Register Byte MSB** No. 5 0 1 Counter 1 Count Register Byte No. 6 LSB 1 0 Counter 2 **Count Register Byte** No. 7 MSB 1 0 Counter 2 **Count Register Byte** No. 8 LSB 0 0 Counter 0 **Count Register Byte** No. 9 MSB 0 0 Counter 0

### NOTE:

The exclusive addresses of each counter's count register make the task of programming the 8253 a very simple matter, and maximum effective use of the device will result if this feature is fully initilized.

Figure 9. Alternate Programming Formats

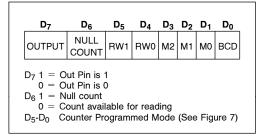

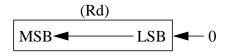

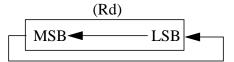

## **Read Operations**

In most counter applications it becomes necessary to read the value of the count in progress and make a computational decision based on this quantity. Event counters are probably the most common application that uses this function. The 8253 contains logic that will allow the programmer to easily read the contents of any of the three counters without disturbing the actual count in progress.

There are two methods that the programmer can use to read the value of the counters. The first method involves the use of simple I/O read operations of the selected counter. By controlling the A0, A1 inputs to the 8253 the programmer can select the counter to be read (remember that no read operation of the mode register is allowed A0, A1-11). The only requirement with this method is that in order to assure a stable count reading the actual operation of the selected counter *must be inhibited* either by controlling the Gate input or by external logic that inhibits the clock input. The contents of the counter selected will be available as follows:

First I/O Read contains the least significant byte (LSB).

Second I/O Read contains the most significant byte (MSB).

Due to the internal logic of the 8253 it is absolutely necessary to complete the entire reading procedure, If two bytes are programmed to be read, then two bytes *must* be read before any loading WR command can be sent to the same counter.

### **Read Operation Chart**

| A1 | A0 | RD | · · · · · · · · · · · · · · · · · · · |

|----|----|----|---------------------------------------|

| 0  | 0  | 0  | Read Counter No. 0                    |

| 0  | 1  | 0  | Read Counter No. 1                    |

| 1  | 0  | 0  | Read Counter No. 2                    |

| 1  | 1  | 0  | llegal                                |

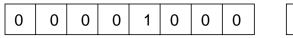

### **Reading While Counting**

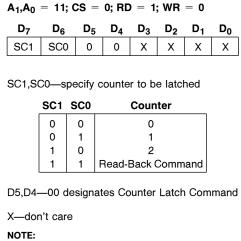

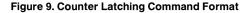

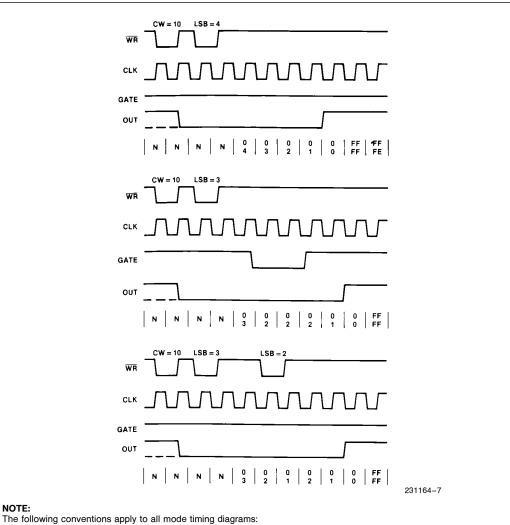

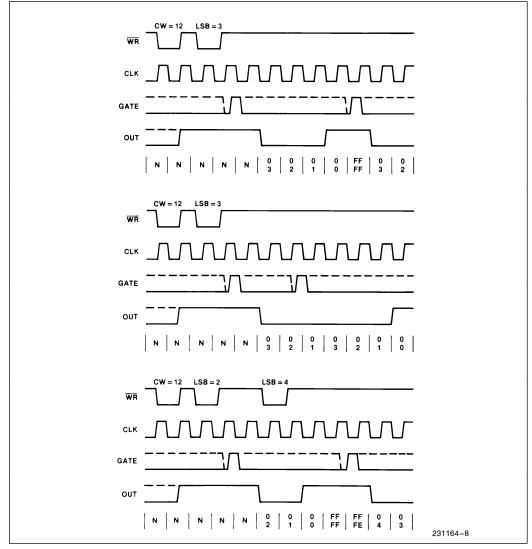

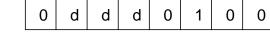

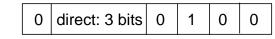

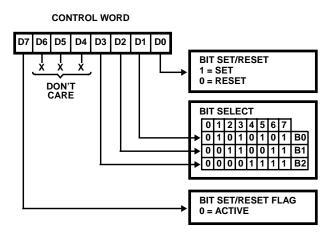

In order for the programmer to read the contents of any counter without effecting or disturbing the counting operation the 8253 has special internal logic that can be accessed using simple WR commands to the MODE register. Basically, when the programmer wishes to read the contents of a selected counter "on the fly" he loads the MODE register with a special code which latches the present count value into a storage register so that its contents contain an accurate, stable quantity. The programmer then issues a normal read command to the selected counter and the contents of the latched register is available.

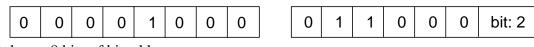

## **MODE Register for Latching Count**

A0, A1 = 11

| $n_{0}, n_{1}$ |     |    |    |    |    |    |    |

|----------------|-----|----|----|----|----|----|----|

| D7             | D6  | D5 | D4 | D3 | D2 | D1 | D0 |

| SC1            | SC0 | 0  | 0  | Х  | Х  | Χ. | X  |

SC1, SC0--- specify counter to be latched.

D5, D4 — 00 designates counter latching operation.

- don't care.

The same limitation applies to this mode of reading the counter as the previous method. That is, it is mandatory to complete the entire read operation as programmed. This command has no effect on the counter's mode.

Х

intel

## ABSOLUTE MAXIMUM RATINGS\*

| Ambient Temperature Under Bi                 | as0°C to 70°C  |

|----------------------------------------------|----------------|

| Storage Temperature                          | 65°C to +150°C |

| Voltage On Any Pin<br>with Respect to Ground | –0.5V to 7V    |

| Power Dissipation                            | 1 Watt         |

\*Notice: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

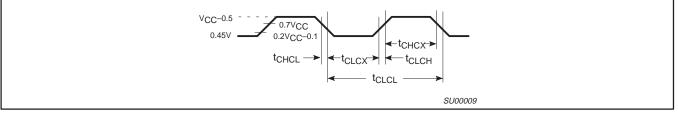

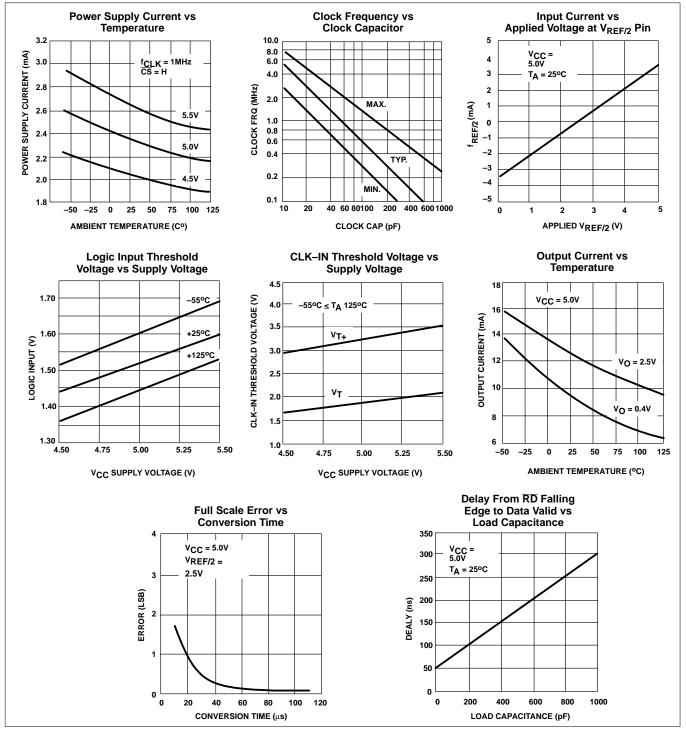

### **D.C. CHARACTERISTICS** $T_A = 0^{\circ}C$ to 70°C, $V_{CC} = 5V \pm 10\%^*$

| Symbol          | Parameter                      | Min  | Мах                | Unit | Test Conditions             |

|-----------------|--------------------------------|------|--------------------|------|-----------------------------|

| VIL             | Input Low Voltage              | -0.5 | 0.8                | V    |                             |

| VIH             | Input High Voltage             | 2.2  | $V_{\rm CC}$ + .5V | V    |                             |

| V <sub>OL</sub> | Output Low Voltage             | •    | 0.45               | V    | (Note 1)                    |

| V <sub>OH</sub> | Output High Voltage            | 2.4  |                    | V    | (Note 2)                    |

| ۱ <sub>۱L</sub> | Input Load Current             |      | ±10                | μΑ   | $V_{IN} = V_{CC}$ to 0V     |

| IOFL            | Output Float Leakage           |      | ±10                | μΑ   | $V_{OUT} = V_{CC}$ to 0.45V |

| lcc             | V <sub>CC</sub> Supply Current |      | 140                | mA   | •                           |

## **CAPACITANCE** $T_A = 25^{\circ}C$ , $V_{CC} = GND = 0V$

| Symbol           | Parameter         | Min | Тур | Max | Unit | Test Conditions                      |

|------------------|-------------------|-----|-----|-----|------|--------------------------------------|

| CIN              | Input Capacitance |     |     | 10  | pF   | fc = 1 MHz                           |

| C <sub>I/O</sub> | I/O Capacitance   |     |     | 20  | pF   | Unmeasured pins returned to $V_{SS}$ |

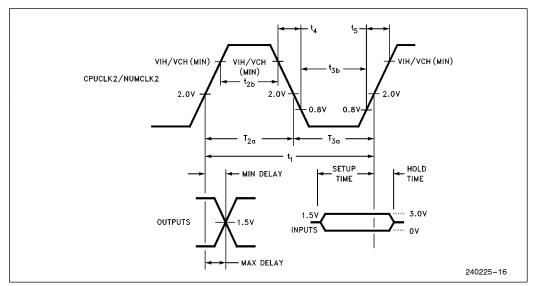

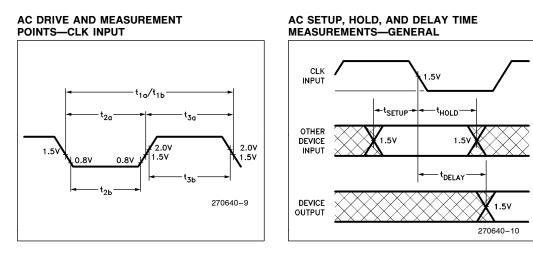

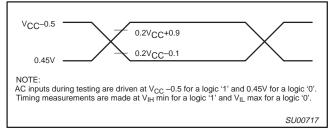

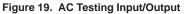

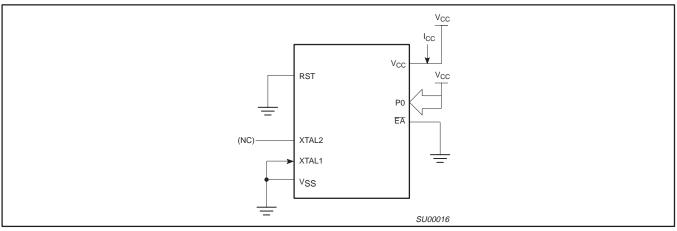

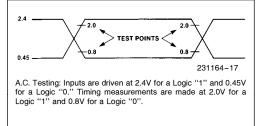

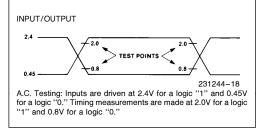

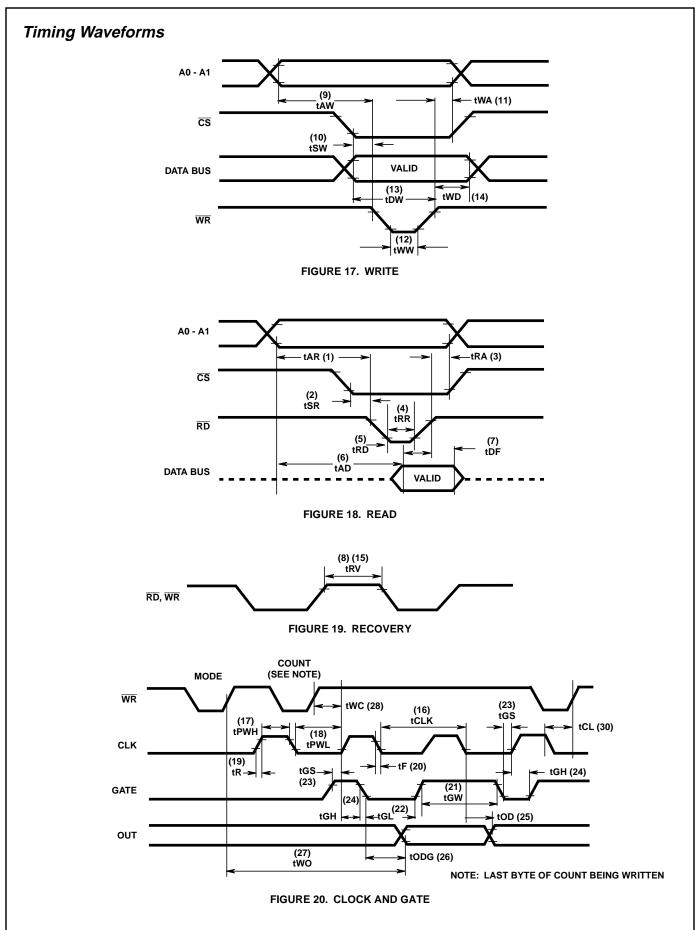

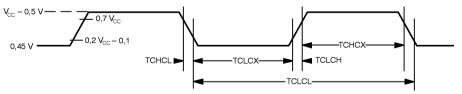

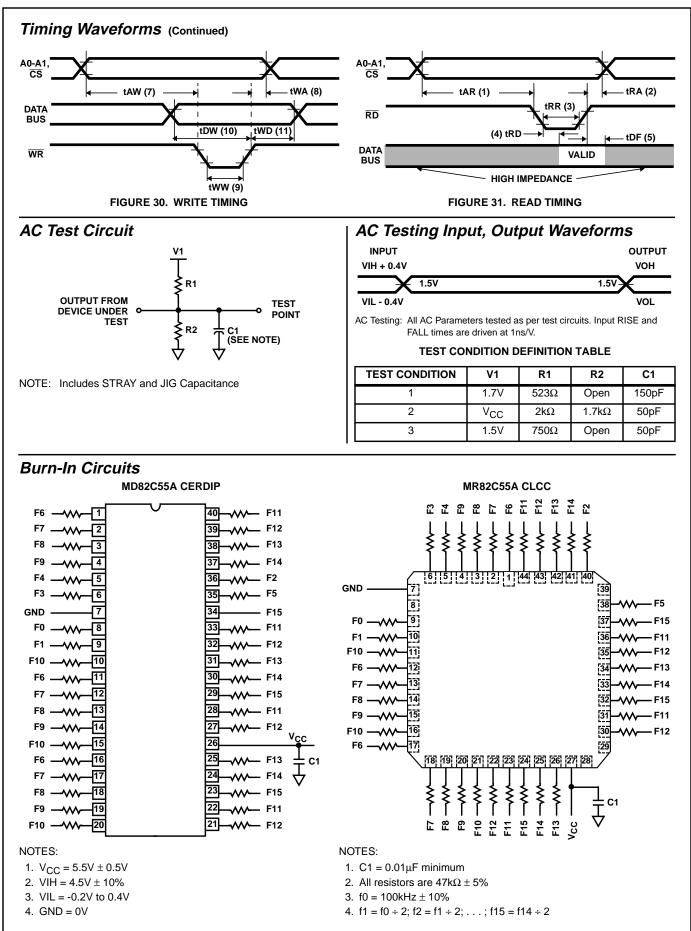

### A.C. CHARACTERISTICS $T_A = 0^{\circ}C$ to 70°C, $V_{CC} = 5.0V \pm 10^{\circ}$ , GND = 0V\*

### Bus Parameters<sup>(3)</sup>

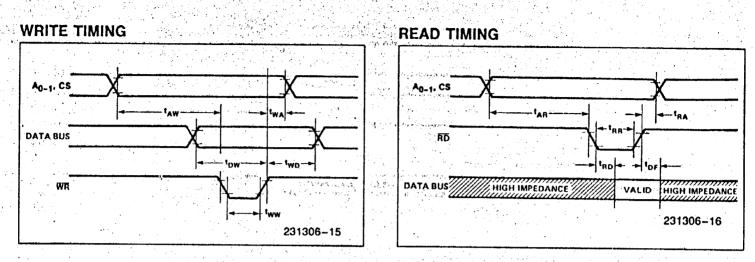

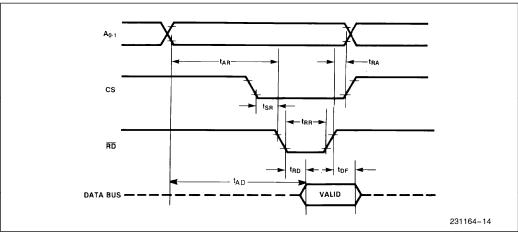

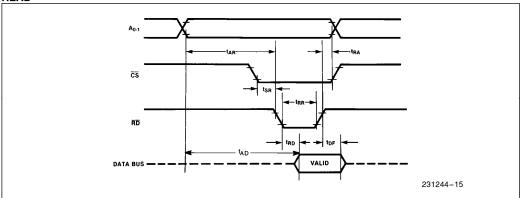

## READ CYCLE

| Symbol          |                                                            | 8253 |     | 8253-5 |     |       |

|-----------------|------------------------------------------------------------|------|-----|--------|-----|-------|

|                 | Parameter                                                  | Min  | Max | Min    | Max | Unit  |

| t <sub>AR</sub> | Address Stable before READ                                 | 50   |     | 30     |     | ns    |

| t <sub>RA</sub> | Address Hold Time for READ                                 | 5    |     | 5      |     | ns    |

| t <sub>RR</sub> | READ Pulse Width                                           | 400  |     | 300    |     | ns    |

| t <sub>RD</sub> | Data Delay from READ(4)                                    |      | 300 |        | 200 | ns    |

| t <sub>DF</sub> | READ to Data Floating                                      | 25   | 125 | 25     | 100 | ns ns |

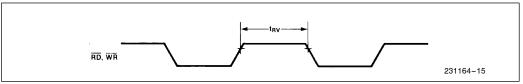

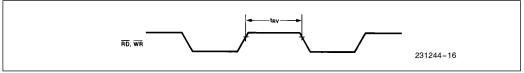

| t <sub>RV</sub> | Recovery Time between READ<br>and Any Other Control Signal | 1    |     | 1      |     | μs    |

8253/8253-5

## A.C. CHARACTERISTICS (Continued)

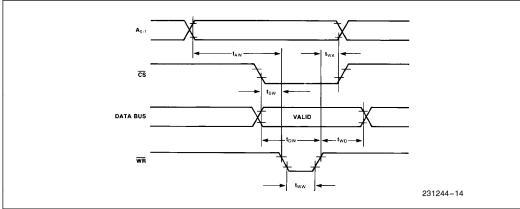

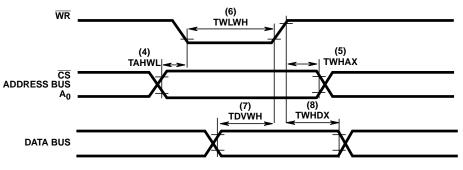

### WRITE CYCLE

| Symbol          | Parameter                                                   | 8253 |        | 8253-5       |     |      |

|-----------------|-------------------------------------------------------------|------|--------|--------------|-----|------|

|                 |                                                             | Min  | Max    | Min          | Max | Unit |

| tAW             | Address Stable before WRITE                                 | 50   |        | 30           | v . | ns   |

| twA             | Address Hold Time for WRITE                                 | 30   | *.<br> | 30           |     | ns   |

| tww             | WRITE Pulse Width                                           | 400  |        | 300          |     | ns   |

| t <sub>DW</sub> | Data Set Up Time for WRITE                                  | 300  |        | 250          |     | · ns |

| twp             | Data Hold Time for WRITE                                    | 40   |        | 30           |     | ns   |

| t <sub>RV</sub> | Recovery Time between WRITE<br>and Any Other Control Signal | 1    |        | (11)<br>(11) |     | μs   |

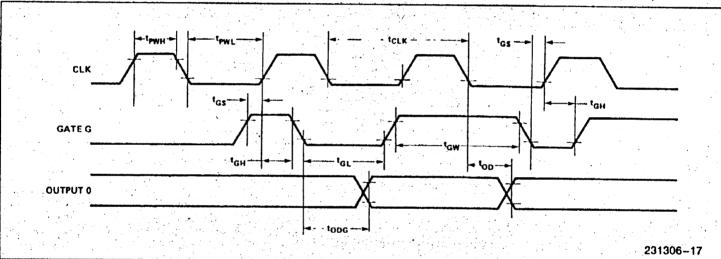

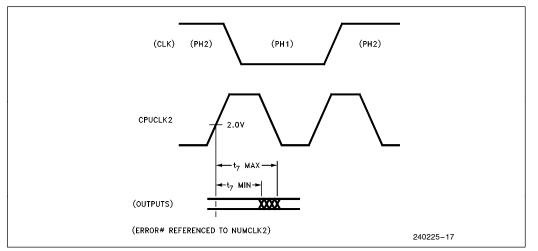

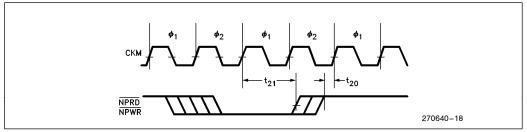

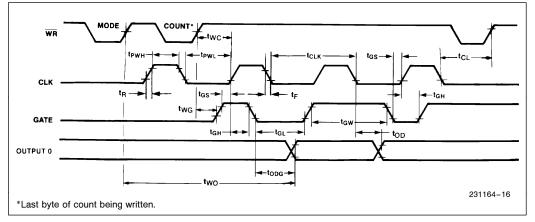

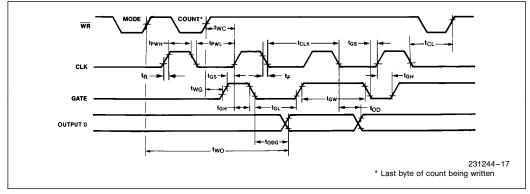

### **CLOCK AND GATE TIMING**

| Symbol           | Parameter                                          | 8253 |     | 8253-5 |     |      |

|------------------|----------------------------------------------------|------|-----|--------|-----|------|

|                  |                                                    | Min  | Max | Min    | Max | Unit |

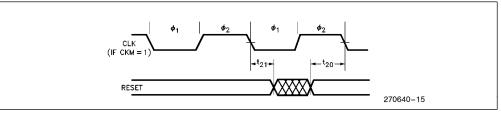

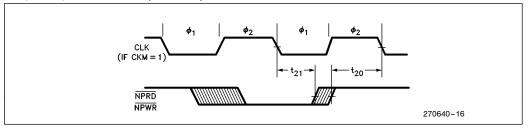

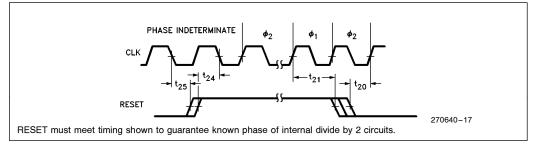

| t <sub>CLK</sub> | Clock Period                                       | 380  | dc  | 380    | dc  | ns   |

| tpwH             | High Pulse Width                                   | 230  |     | 230    |     | ns   |

| t <sub>PWL</sub> | Low Pulse Width                                    | 150  |     | 150    |     | ns   |

| t <sub>GW</sub>  | Gate Width High                                    | 150  |     | 150    |     | ns   |

| t <sub>GL</sub>  | Gate Width Low                                     | 100  |     | 100    |     | ns   |

| t <sub>GS</sub>  | Gate Set Up Time to CLK 个                          | 1`00 |     | 100    |     | ns   |

| t <sub>GH</sub>  | Gate Hold Time after CLK ↑                         | 50   |     | 50     |     | ns . |

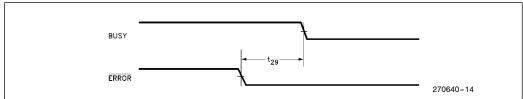

| top              | Output Delay from CLK $\downarrow$ <sup>(4)</sup>  |      | 400 |        | 400 | ns   |

| todg             | Output Delay from Gate $\downarrow$ <sup>(4)</sup> |      | 300 |        | 300 | ns   |

### NOTES:

1.  $I_{OL} = 2.2 \text{ mA.}$ 2.  $I_{OH} = -400 \mu \text{A.}$

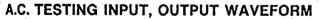

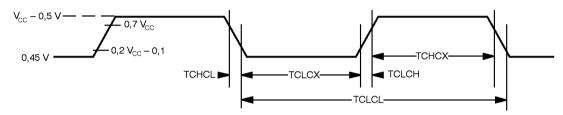

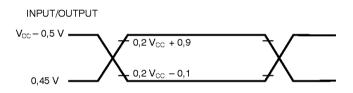

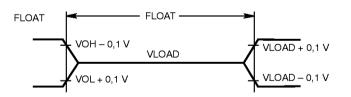

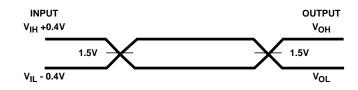

3. AC timings measured at V<sub>OH</sub> 2.2, V<sub>OL</sub> = 0.8.

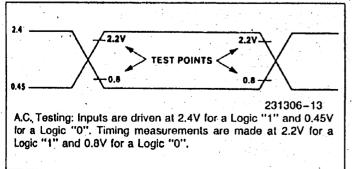

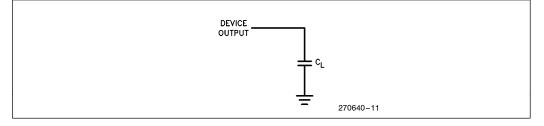

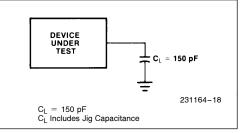

4.  $C_L = 150 \text{ pF}$ .

\*For Extended Temperature EXPRESS, use M8253 electrical parameters.

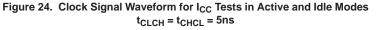

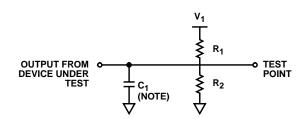

### A.C. TESTING LOAD CIRCUIT

General Con

## WAVEFORMS

inte

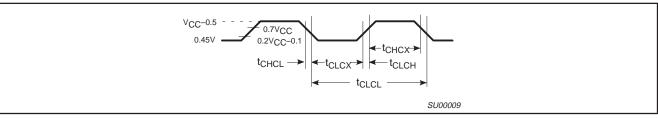

### CLOCK AND GATE TIMING

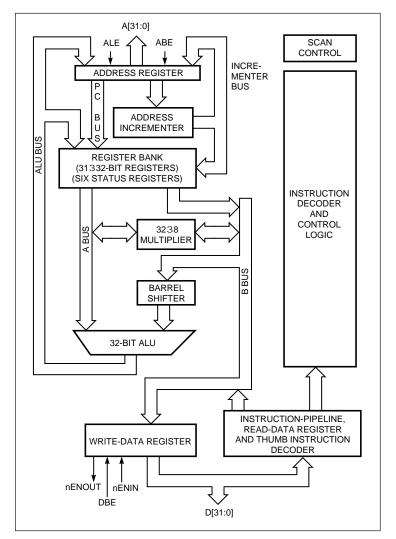

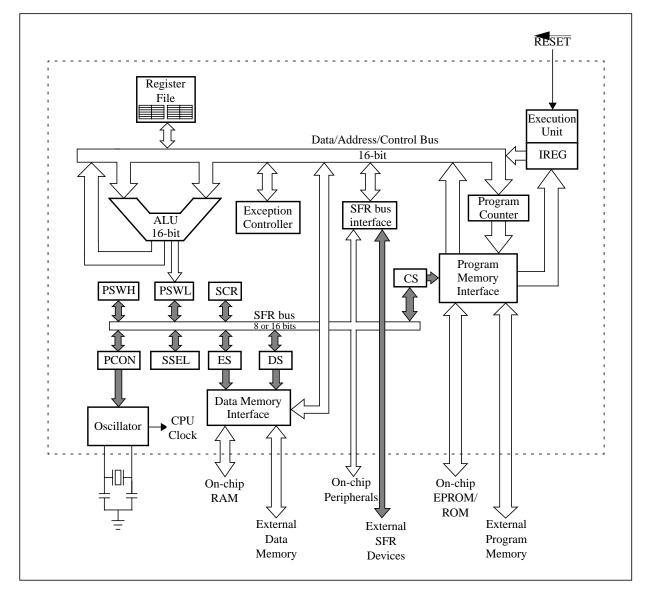

# ARM processors

ARM designs mP cores and cached macrocells for its licensees. Partners offering ASICs with embedded ARM cores are Atmel/ES2, Cirrus Logic, Mitel, IBM, LG Semicon (www. Igsemicon.co.kr/), LSI Logic, Lucent (www.lucent.com), National Semiconductor, NEC, Oki, Samsung, Seiko Epson (www.epson.co.jp/), Sharp, Symbios Logic (www.symbios. com), TI, and VLSI. Some partners offer the ARM core in embedded products for vertical markets.

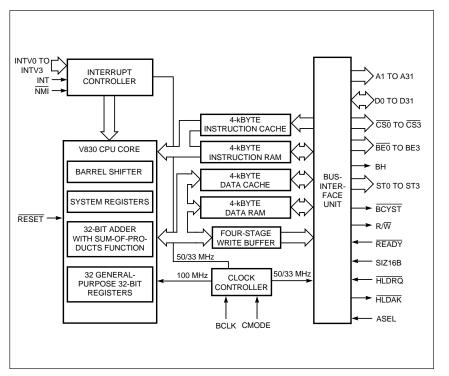

ARM processors comprise the ARM7 Thumb, ARM9 Thumb, and StrongARM product families. (ARM will announce ARM10 in October.) All the processors support the ARM instruction set, providing full software compatibility over a range of performance and cost.

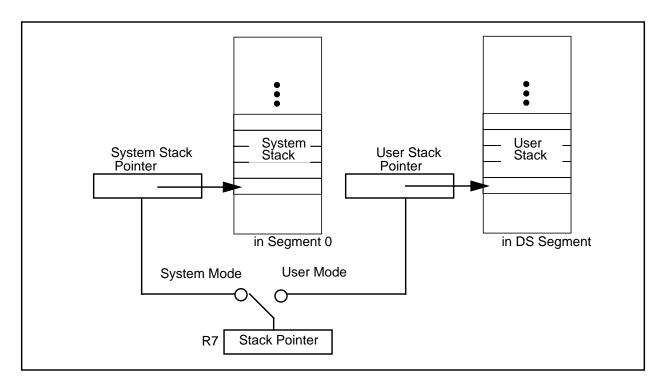

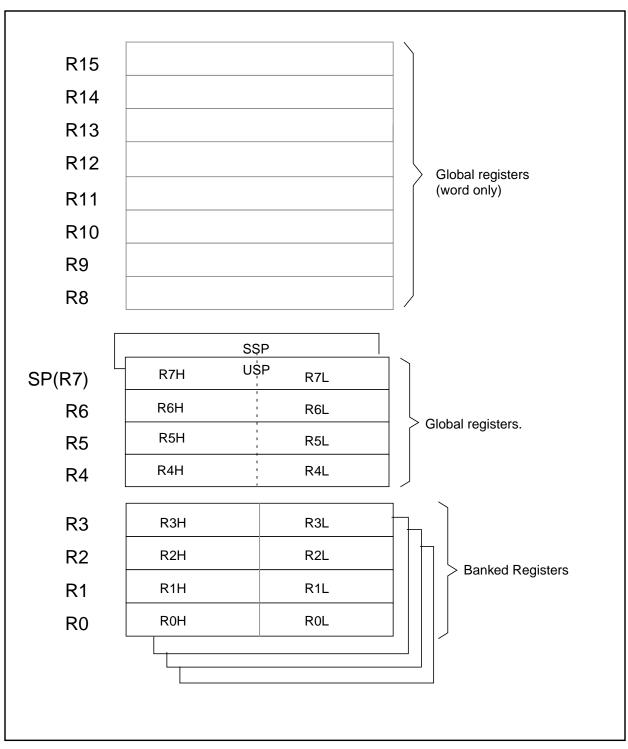

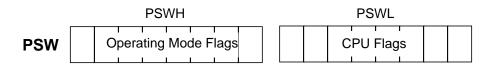

The ARM cores and cached macrocells implement a load/store architecture and have 31 general-purpose registers with 16 simultaneously visible. A fast interrupt has a minimum latency of four processor cycles and uses seven private registers to minimize state-saving overhead. All registers, excluding the program counter, are general-purpose, although a set of conventions, the ARM Procedure Call Standard, governs the registers' use for C compatibility.

The ARM cores and cached macrocells support user and supervisor modes for controlling access; they handle interrupt-request, fast-interrupt-request, abort, and undefined exception-processing modes. Modes use register windows to overlay some of the 16 general-purpose registers.

The Thumb architectural extension is primarily a 16-bit subset of the 32-bit instruction set. On execution, the Thumb module, residing within the instruction pipeline, decompresses the 16-bit instructions back to 32-bit instructions without added delay. The Thumb module adds about 6% to the core's die size but helps increase code density and overcome the waste from using 32-bit fixed-length instructions.

The bus clock for most ARM cached macrocells can be synchronous or asynchronous with respect to the internal cache clock. All ARM cached macrocells contain a write buffer, which lets execution continue while writes are pending. The buffer holds 8 words at four independent addresses.

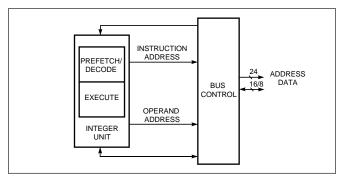

The ARM7 Thumb family comprises the ARM7TDMI core and ARM7x0T cached macrocells. This architecture, Version 4T, consists of a three-stage—fetch, decode, and execute—

pipeline to achieve single-cycle instruction execution. All cores use an 8-bit Booth multiplier, which executes in five or fewer cycles for 32332-bit multiply and offers 64-bit multiplication. The ARM740T integrates a simplified memory-management unit (MMU) that allows you to specify eight memory areas by individually programming their base address, size, cache control, write-buffer control, and access permissions. This approach simplifies the programmer model and reduces the core size to less than that of the ARM710T and ARM720T.

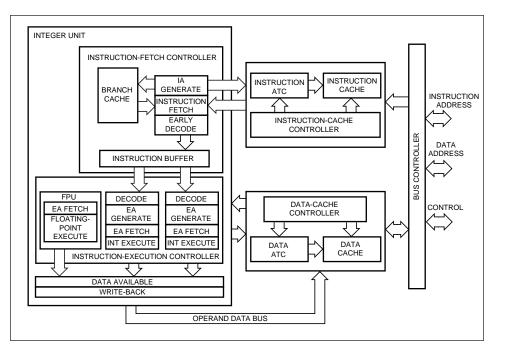

ARM based the ARM9 Thumb family, available as the ARM940T, on the ARM9TDMI core. The core is also an implementation of the ARM Version 4T architecture but with a five-stage—fetch, decode, execute, memory, and write-back—pipeline. The additional pipeline depth and design implementation double the performance over the ARM7 Thumb cores. The bus architecture also differs, using a Harvard approach compared with the ARM7 Thumb core's von Neumann architecture. The ARM940T implements the same MMU as the ARM740T. You can use the cache in write-through and -back modes; write-back mode reduces the number of external transactions from the core.

StrongARM uses a five-stage pipeline and Harvard architecture and supports Version 4 of the ARM architecture. It provides a fourfold increase in performance over the ARM7 Thumb cores. Intel now produces and develops StrongARM, which is available as the standard SA-110 processor and as part of custom logic products.

The cores avoid excess pipeline flushes—Strong-ARM by using early branch execution and ARM7 by using static branch prediction, always taking the rear branch as in a loop. The SA-110 has separate instruction and data MMUs. The translation-look-aside buffers (TLBs) have 32 entries that can each map a segment, large page, or small page and use a round-robin replacement algorithm. The data TLB supports both

## ARM processors (continued)

flush-all and flush-single-entry functions, and the instruction TLB supports only the flush-all function.

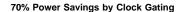

**Power management:** All the ARM processor cores and cached macrocells are static designs. Furthermore, the designs use gated clocks and transparent latches, clocking the logic only during an operation (but not during a wait state).

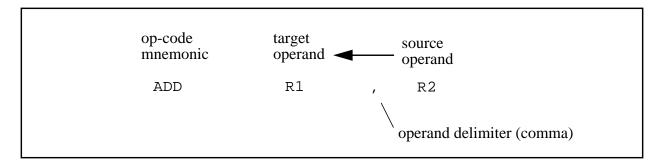

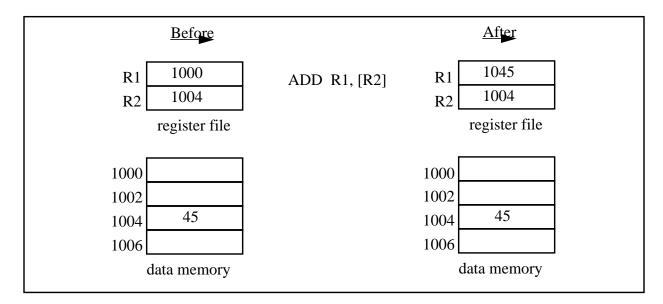

Special instructions: ARM has 11 basic types of fixed-length instructions, which execute conditionally—not just branch—and reduce the need for short pipeline-flushing branches. A not-taken instruction executes in one cycle. Taken branches incur a three-cycle delay. The 16 executioncondition codes include equal, not equal, always, negative, and overflow. The ARM lacks explicit shift instructions; instead, all ALU operations can perform an optional shift operation in one execution cycle. The processors have blockdata-transfer instructions to load and store data from any subset of the 16 general-purpose registers.

ARM processors lack an integer-divide instruction; however, the chips have multiply and multiply-accumulate (MAC) instructions. The MAC instruction speeds math-intensive applications. ARM processors can synthesize division and multiplication by a constant using sequences of one or more shift-and-add or shift-and-subtract instructions. (For example, division by 4 and multiplication by 5 each take one cycle.)

Special on-chip peripherals: The ARM7 Thumb and ARM9 Thumb processor cores have integrated EmbeddedICE logic, allowing you to debug the core via a JTAG interface. The ARM Advanced Microcontroller Bus Architecture (AMBA) interface is the standard bus interface to ARM7 Thumb and ARM9 Thumb cached macrocells.

Development tools: ARM offers a variety of software-development tools and hardware-development platforms, including the ARMUIator instruction-set emulator. A range of thirdparty development tools and operating systems also support the ARM architecture. Cygnus Solutions (www.cygnus.com), Embedded Performance (www.episupport.com), Green Hills Software (www.ghs.com), Metaware (www.metaware.com), Microtec (www.microtec.com), Microware Systems Corp (www.microware.com), and Wind River (www.windriver. com) offer development-tool chains and compilers. Accelerated Technology (www.atinucleus.com), Chorus Systems (www.sun.com), CMX Co (www.cmx.com), Embedded Performance, Etnoteam (www.etnoteam.it/), Geoworks (www.geoworks.com), Integrated Systems (www.isi.com), Microsoft (www.microsoft.com), Microware, Psion Software (www.psion.com), US Software (www.uss.com), and Wind River provide RTOS support. Hewlett-Packard (www. hp.com), Lauterbach (www.lauterbach.com), and Yokogawa Digital Corp (www.yokogawa.com) offer a debugger and an in-circuit emulator.

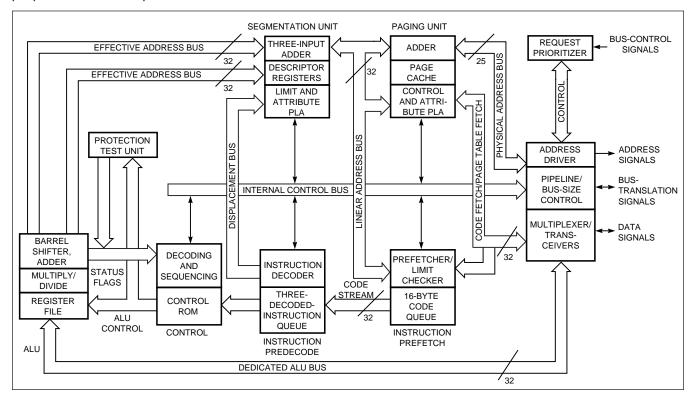

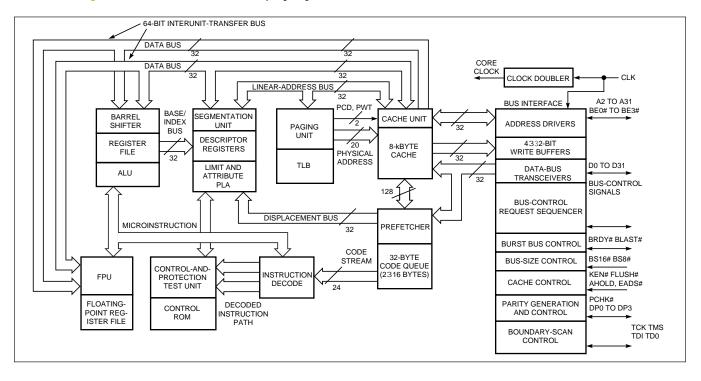

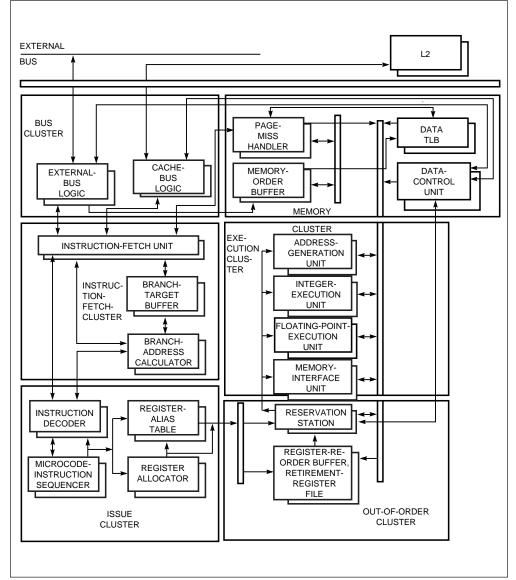

# 80386

The 386 has disappeared from the desktop-PC market but has developed a strong presence in embedded-PC applications. Register-based, the 80386 architecture has four general-purpose registers, four index/pointer registers, six 16-bit segment registers, and two 32-bit status and control registers. Intel's 8086 designers used 64-kbyte segments to extend addressing to 1 Mbyte. The 80386 also uses segmentation; however, because the general-purpose and index/pointer registers are now 32 bits, the segment limits extend to the full 4-Gbyte addressing range, and a segment register references a segment descriptor with a 32-bit base address. These descriptors also carry addressing-range and protection limits to prevent data accesses into code, data that executes as code, and access to inner privilege levels by outer levels.

Hardware-descriptor registers hold segment-access rights and segment-base address and size limits. In protected-mode addressing, a 16-bit selector points to a segment descriptor and furnishes a base address. The base address adds to the 32bit effective address, producing a 32-bit linear address, which the 80386 then uses as a physical or linear-page address.

The 386 has four code/data breakpoint registers and two control registers for debugging. You can set the breakpoint registers with addresses for halting execution on a program or data access.

Power management: System-management mode (SMM), a power-management mechanism, enables code to control CPU power without rewriting or revamping operating software. The CPU enters SMM via a hardware interrupt, the system-management interrupt (SMI); the SMI code can set SMMs to reduce chip power dissipation. Integrated versions of the 386, including Intel's 386EX, have idle and power-down modes: Idle discontinues CPU processing but keeps peripherals active, and power-down shuts down the entire

chip. AMD's 386SC300 chip has low-speed mode, during which the CPU goes to 0.5 MHz; doze, which stops the CPU, system, and DMA clocks; sleep, which stops additional clocks and peripherals; and suspend, which stops everything except the real-time clock and memory.

Special instructions: The 386 instruction set is a superset of the 8086/186. To support SMM, the 386 has seven additional instructions, such as RSM (resume), which causes the processor to resume from SMM.

Special on-chip peripherals: Intel's 386EX peripherals include a serial-I/O unit, a chip select, a clock generator, a DMA- and bus-arbitrator unit, a DRAM-refresh-control unit, an interrupt-control unit, a memory-management unit, and a parallel-I/O unit. AMD's ElanSC300 combines an Am386 CPU with a PC/AT chip set and essential embedded-PC peripherals. The ElanSC300 also includes mobile-computing peripherals, such as PLL clock generators, PCMCIA-card support, LCD-graphics control, a memory controller, DMA and interrupt controllers, a real-time clock, a serial port, and a parallel port.

Development tools: Numerous third-party vendors support the 386 architecture. They provide tools that include assemblers, compilers, linkers/locators, remote software debuggers, software simulators, and integrated design environments for software development. In addition, several vendors provide utilities, such as flash-programming, device-driver, and flashtranslation-layer implementations. Hardware tools include in-circuit emulators, logic analyzers, evaluation platforms, and single-board computers. Operating-system support includes DOS and windowed OSs and a variety of real-time OSs from small, royalty-free microkernels to feature-rich graphical-user-interface RTOSs.

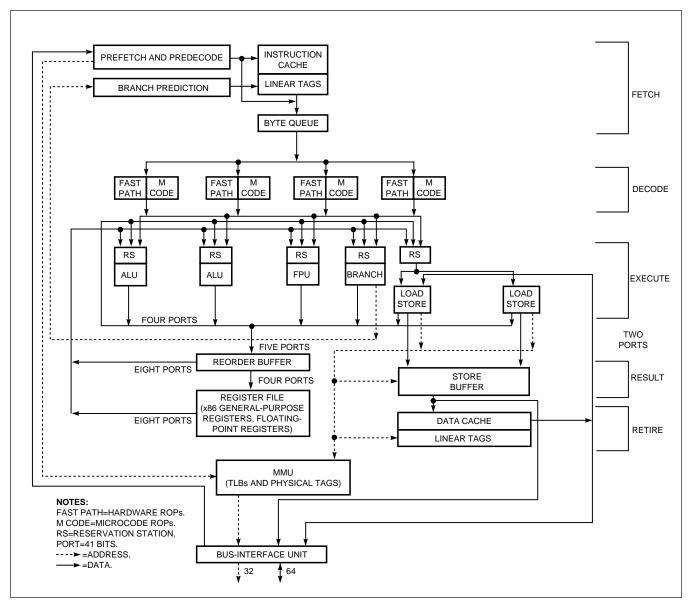

# 80486

The 486 builds on the 386 architecture by adding a more efficient memory bus; an on-chip floating-point unit; an onchip, unified, Level 1 cache; and a RISC-like implementation for the core load/store instructions. The 32-bit 80486 implementation retains the i386's complex instruction set but relies on a pipelined RISC-like implementation to speed execution for simple load/store instructions. The standard 486 microarchitecture has a five-stage pipeline and uses two of those stages, decoder stages D1 and D2, to decode the complex instruction set.

The 486 chips use 1- to 15-byte-long instructions for complex operations. The two decoder stages give the hardware time to delineate and decode the instructions waiting in the instruction queue. The instruction or byte-code queue holds 32 bytes for decoding. By fetching 4 words at a time from offchip or local memory, the hardware minimizes contention between data and instruction accesses of the cache. To speed processing, the hardware loads and writes cache lines in 4word bursts.

The DX4 has a unified cache that is four-way set-associative and implements a write-through policy: Writes to cache pass through to memory, which raises memory bandwidth. The 486's bus and cache implement a bus-snooping protocol for multiprocessor operation. The bus is more efficient than that of the 386 and has a two-clock single read or write; 4word read bursts take five cycles and constitute most 486 bus accesses. The processors also support secondary Level 2 cache for both single-processor and multiprocessor operation, as well as write-through/write-back protocols.

The 486 has four code/data breakpoint registers and two control registers for debugging. You can set the breakpoint registers with addresses for halting execution on a program or data access.

Power management: The standard 486 employs system-

management mode (SMM) for power management, which enables code to control CPU power without rewriting or revamping operating software. The CPU enters SMM via a hardware interrupt, the system-management interrupt (SMI); the SMI code can set SMMs to reduce chip power dissipation. A halt instruction powers down most of the CPU's logic.

Special instructions: The 486 instruction set builds upon that of the 80386, adding instructions such as byte swap, exchange and add, compare and exchange, invalidate data cache, write-back and invalidate data cache, invalidate translation-look-aside-buffer entry, processor identification, and SMM resume.

Special on-chip peripherals: AMD's ElanSC400 microcontroller combines an Am486 CPU with a PC/AT chip set and essential embedded-PC peripherals. The ElanSC400 also includes mobile-computing peripherals, such as PLL clock generators, PCMCIA-card support, LCD-graphics control, a memory controller, DMA and interrupt controllers, a realtime clock, a serial port, and a parallel port.

**Development tools:** Most of the tool support for the 486 is the same as that for the 386. AMD, Intel, and National offer evaluation kits for each of their 486 processors. For example, AMD's \$950 mforCE (micro for CE) demonstration system for mobile and embedded product development uses the AMD's ElanSC400 microcontroller and the QNX (www.qnx.com) Realtime OS or Microsoft (www.microsoft.com) Windows CE OS. The board contains an external matrix scan keyboard, a flash minicard slot, a PCMCIA type 2 slot, an IrDA interface, a serial port, a 10-bit digitizer controller for pen input, an audio chip, and 4 Mbytes of ROM and DRAM.

Second sources: There are no pin-compatible second sources for the 80486. AMD, Intel, and STMicroelectronics act as second sources for some implementations.

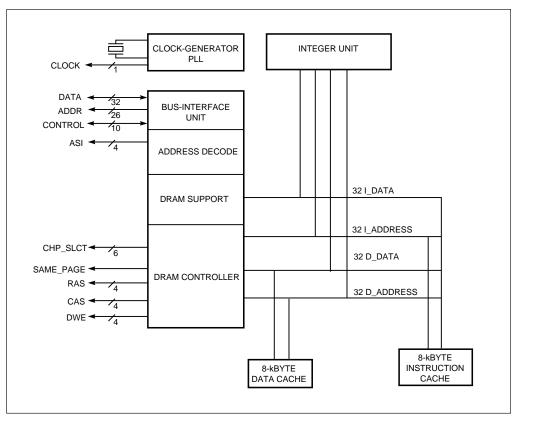

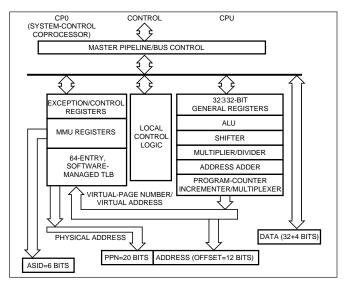

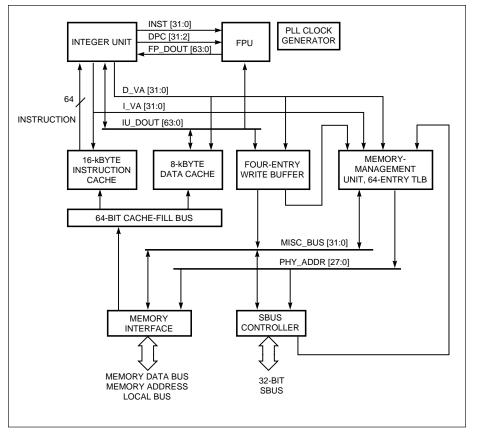

# Fujitsu SPARClite

Fujitsu based its MB8683x, or SPARClite, family on V8E spec, SPARC International's (www.sparc.com) embedded specification. The family features a 32-bit ALU and uses a load/store architecture with a register stack of 136 32-bit registers. (The 86933H chips have 104.) Eight reserved registers hold global values. The remaining registers arrange into eight overlapping register windows, one for each subroutine. This setup speeds procedure calls and interrupt processing. Multiple contexts can be present concurrently by limiting the number of registers for a task.

Fujitsu engineers extended the SPARC pipeline for the SPARClite family to fetch, decode, execute, memory, and write-back stages. The memory stage minimizes the effects of load/store operations and reduces a load/store to onecycle execution. The stage is

idle for nonload/store operations.

All SPARClite mPs have separate data and instruction caches. The caches are two-way set-associative and have 16or 32-byte cache lines. You can lock and not swap out critical cache lines on chip. The MB86832 also incorporates a debug-support unit and an emulator bus, which makes instruction streams visible even in on-chip cache. Debugging registers hold data values or addresses for individual and range breakpoints.

The SPARClite processors run with DRAM, synchronous DRAM, SRAM, and ROM/EPROM. The memory interface handles page-mode DRAM for low-cost, high-speed access using a 32-byte burst mode. The memory interface includes a refresh generator for DRAMs, programmable wait states for slower memory, and programmable chip selects for memory banking. Boot-up memory interfaces are programmable; SPARClite CPUs can boot from 8-, 16-, or 32-bit ROM/ EPROM.

**Power management:** SPARClite processors incorporate power-down modes, and a power-management register controls shutdown of the floating-point unit.

Special instructions: The SPARClite implements the SPARC V8 specification, which includes a hardware multiply instruction and a software division using divide by 4. Other special instructions include scan word looking for first changed bit or first one or zero, load/store double word, save/restore caller (uses register windows), tagged add/subtract (generates overflow if most significant bits 0 and 1 are not 0), atomic math and swap, and generate trap from conditions.

Special on-chip peripherals: SPARClite processors come with a 24-bit timer that has an 8-bit prescaler and a 16-bit counter. You can program this counter to operate in periodic-interrupt, time-out-interrupt, or square-wave-generator mode. The mP's debug-and-support unit (DSU) comprises two 4-bit emulator buses for data and status and two control signals that enable and set the breakpoint of an in-circuit emulator for hardware debugging and software development. The SPARClite's DSU has six breakpoint-descriptor registers and supports five hardware-monitoring debugging modes.

Development tools: SPARClite shares many of the development tools that support the SPARC architecture, including compilers and debuggers. Fujitsu supplies \$89 evaluation kits and full-featured evaluation boards and monitors. Fulitsu works with Wind River Systems (www.windriver.com), Chorus Systems (www.sun.com), Accelerated Technology (www.atinucleus.com), Microtec (www.microtec.com), JMI (www.jmi.com), Integrated Systems (www.isi.com), and Lynx (www.lynx.com) for RTOS support. These vendors also supply system calls and library routines, many device drivers, and network protocols. Cygnus (www.cygnus.com), Wind River, and Green Hills Software (www.ghs.com) development environments also support SPARClite. Orion Instruments (www.yokogawa.com) in-circuit emulators support SPARClite-based system development. US Software (www. ussw.com) and Log Point (www.logpoint.com) offer floatingpoint libraries for SPARClite.

Second sources: There are no second sources for SPARClite.

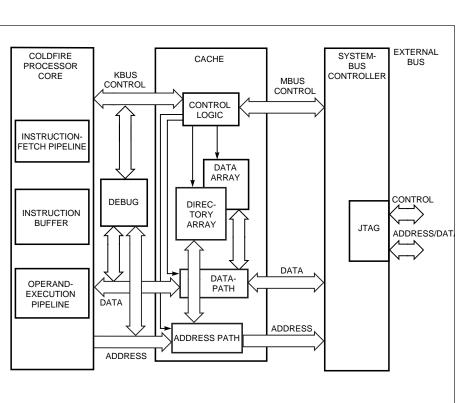

# Hitachi SuperH Series

The SuperH Series comprises the SH-1, SH-2, SH-3, and SH-4 series of RISC mPs, mCs, and ASIC cores. The SH-1, -2, and -3 employ a fetch, decode, execute, memory-access, and write-back-to-register pipeline. Hitachi built the devices around 25 32-bit registers that you access using load/store instructions. These registers comprise 16 general registers (the SH-3 has eight 32-bit shadow registers for context switching), five control registers, and four system registers. Depending on the chip, the interrupt latency can be as low as seven clock cycles. The chips use 32-bit datapaths to internally move data, but all versions use a flexible external bus width. The SuperH family also has devices with single-cycle mask ROM and one-time-programmable and flash memory with densities as high as 256 kbytes, unlike most RISC families.

Although devices in the SH series have a similar core, significant differences exist. The major differences between SH-1 and SH-2 are that the SH-2 features on-chip cache memory, higher speeds, and a 32332-bit multiply-accumulate (MAC) unit. (The SH-1's MAC unit is 16316 bits.) To build the SH-3, Hitachi added to the SH-2 a memory-management unit (MMU), a barrel shifter, and the ability for conditionalbranch instructions to enable or disable the pipeline's delay slot. Disabling the delay slot, although decreasing performance, allows the processor to run more deterministically and reduces the effects of pipeline flushes.

The 200-MHz, two-way-superscalar SH-4 mP includes a 3-D graphics accelerator that Hitachi claims can perform at 1.2 Gflops. This mP has four 32332-bit multipliers fed by two 128-bit buses; it also has four adders. You can load the multipliers with eight operands in one cycle; the mP then adds the results in the next cycle. This hardware performs rotations and transformations on 32-bit, single-precision, floating-point vectors.

SuperH processors use a 16-bit instruction word to achieve compact code. The instruction width limits the number of basic operation codes, handles only 16 general registers, and addresses only two operands. Additionally, only 12 bits are available for an immediate offset; jumps with immediate data must be in 2048-byte hops. However, the SH-3 supports FARrelative branches to support position-independent code. Although these restrictions lead to more instructions per task, the overall result is significantly smaller code.

The SH-1 mPs can operate from external memory or from on-chip program memory at a CPU frequency of 20 MHz. The 16-bit-wide external-memory bus can supply the CPU with instructions from SRAM or fast DRAM on each cycle. If the processor is operating from external memory, each data access to external memory may take an additional one to two cycles.

Instead of on-chip program memory, the SH-2 and SH-3 have a four-way, set-associative on-chip cache (4 kbytes for the SH-2 and 8 kbytes for the SH-3), a 32-bit-wide memory bus for CPU-memory bandwidth as high as 60 MHz with a synchronous-DRAM interface), and a 32-bit divide unit (replacing the first chip's bit-step-divide function on the SH-2). You can reconfigure the cache as a two-way, set-associative cache and 2 kbytes (SH-2) or 4 kbytes (SH-3) of user-configurable RAM. The external-memory bus supports multiprocessing; it has bus arbitration for multiple masters. The SH-3 also has a unique RTOS feature: If a task or thread crashes, the operating system can gracefully recover and not

have the errant task corrupt other tasks or RTOS environments.

**Power management:** Sleep mode discontinues CPU processing but keeps peripherals active. Standby stops everything but maintains register and cache contents. The SH-2 and -3 provide several clock modes for reducing power; software can adjust the clock rate during program operation. The SH-3's unified cache has a special low-power design that dissipates only 100 mW in operation. The cache sense amps are energized for the cache set that hits while the other three sets stay switched off. The sense amps respond to only a 60-mV differential versus the full 3.3V swing.

**Special instructions:** A 16316-bit MAC instruction (42-bit accumulator) in the SH-1 and a 32332-bit MAC instruction (64-bit accumulator) in the SH-2 and SH-3 provide a fast DSP function. Although Hitachi classifies the architecture as load/store, some instructions reference memory. Delayed branch instructions minimize pipeline disruption. An instruction swaps upper and lower bytes. The SH-4 includes a set of 3-D, floating-point instructions. The SH-DSP, a version of the SH-2, supports 23 32-bit DSP instructions for zero-overhead looping and modulo-addressing support.

**Special on-chip peripherals:** The SH-DSP contains a DSP as an "on-chip peripheral." This DSP unit shares the five-stage pipeline with the integer unit; the DSP is not a coprocessor. The CPU contains a fetch-and-decode unit, which manages the instruction stream for both the integer and DSP units, routing instructions to the appropriate unit (see *EDNs* 1998 "DSP-architecture directory," April 23, 1998, pg 54). Other, more conventional peripherals include memory controllers, a real-time clock, smart-card and serial codec interfaces, IrDA support, a floating-point-unit coprocessor, a hardware division unit, complex multifunction timers, a PCMCIA interface, and an LCD controller.

The SH-3 contains an MMU with a 128-entry translationlook-aside buffer (TLB). The TLB caches virtual-to-physicaladdress translations from user-created page tables to external memory, providing both data protection and virtual memory. Address translation employs a paging system that supports 1- or 4-kbyte pages. The MMU also handles multitasking by providing multiple virtual-memory modes. Thus, each process has its own virtual memory and cannot access the resources of another process or the OS kernel.

**Development tools:** Hitachi and a number of third-party vendors offer development-tool support for the SuperH. Hitachi, Green Hills Software (www.ghs.com), and Cygnus (www.cygnus.com) provide C and C++ compilers. Hitachi, HP (www.hp.com), Orion Instruments (www.yokogawa. com), and Sophia Systems (www.sophia.com) offer in-circuit emulators. Wind River (www.windriver.com), Accelerated Technology Inc (www.atinucleus.com), and Microsoft (www.microsoft.com) provide RTOSs. Other tools include assemblers, ROM emulators, integrated Windows-based development environments, debuggers, floating-point libraries, and networking libraries. Hitachi supports Windows CE development with the \$10,000 D9000, a reconfigurable development platform.

Second sources: Seiko-Epson (www.seiko.com), VLSI, ST-Microelectronics, and Sony (www.sel.sony.com) are licensees.

See *EDN*'s Web-site version, www.ednmag.com, for block diagram.

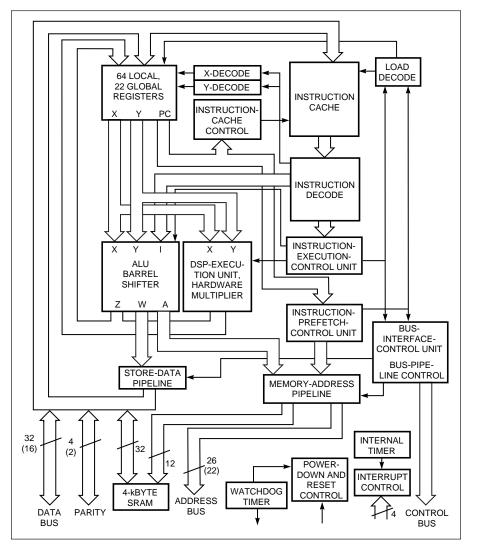

# hyperstone E1-32X

The hyperstone E1-32X combines RISC and DSP technology in one core. The E1-32X has a load/store architecture built around a register set that includes 64 general-purpose local and 22 global registers. Local registers are organized into a 64-word, circular register stack to hold function/subroutine stack frames. The stack is organized into frames of as many as 16 words; the E1-32X keeps current frames on chip and automatically pushes the frame to off-chip memory as the register stack fills and moves frames back on chip as the register stack empties. For fast parameter passing, the current stack frame can overlap the previous one with a variable range. Instructions are 16, 32, or 48 bits wide. The variable-length instructions, which the E1-32X automatically prefetches, provide constants and native addresses as large as 32 bits.

The 4-Gbyte address space divides into four blocks; you can configure each block individually for bus width and timing. You can use these blocks for glueless connection of DRAM, extended-data-out DRAM, SRAM, EPROM, or other memory devices, each with its own timing and bus width. A separate I/O-address space also allows each I/O device to have its own timing.

The integrated DSP unit, working in parallel with the ALU and the load/store unit, can perform DSP calculations while the ALU is performing loop counts, address calculations, or load-and-store operations. The ALU executes its instructions during the

latency cycles of DSP instructions. The DSP unit shares all the E1-32X's functional blocks, including the register set; however, it provides dedicated result registers and 32- and 64-bit hardware accumulators. The DSP unit supports 16- and 32bit data types.

Power management: In automatic power-down mode, only the interrupt logic, clock, and DRAM-refresh logic remain active. Sleep mode also disables DRAM refresh. At 3.3V, current consumption in power-down and sleep modes is less than 2.5 mA and 100 mA, respectively.

**Special instructions:** DSP instructions include multiply, complex and real multiply-accumulate, multiply-subtract, and complex addition/subtraction. Other special instructions include test-leading zeros.

Special on-chip peripherals: Hyperstone's E1-32X contains a DRAM controller that allows you to program page size, refresh rate, timing, and access parameters with an internalmemory register. The controller supports fast-page-mode and extended-data-out DRAMs. The mP also contains a singlecycle-access, 8-kbyte memory, and an I/O- and peripheral-

interface controller. You can use this controller to set the width and timing of the mP's address areas. An integrated PLL allows you to multiply the external clock by a factor as large as 4. Development tools: The vendor offers a development starter kit, a PC-based development board, and the hyICE serial connector for stand-alone operation. The company also provides an ANSI C compiler and DSP library, a source- and task-level debugger, a multitasking real-time kernel, an assembler, a linker, a library manager, and a profiler. Eonic Systems (www.eonic.com) and Etnoteam (www.etnoteam.com) provide RTOS support. Visual Tools (www.etnoteam.it) offers a JPEG embedded-image-compression/decompression library for the hyperstone E1-32X mP. The library supports userdefined subsampling for image quality and compression to the desired size. Hyperstone provides speech compression/decompression algorithms (G.726, G.729, G.723.1, GSM 06.10) and a complete modem. GAO Research (www.gaoresearch.com) offers V.22 modem code.

Second sources: LG Semicon (www.lgsemicon.co.kr) is a licensee.

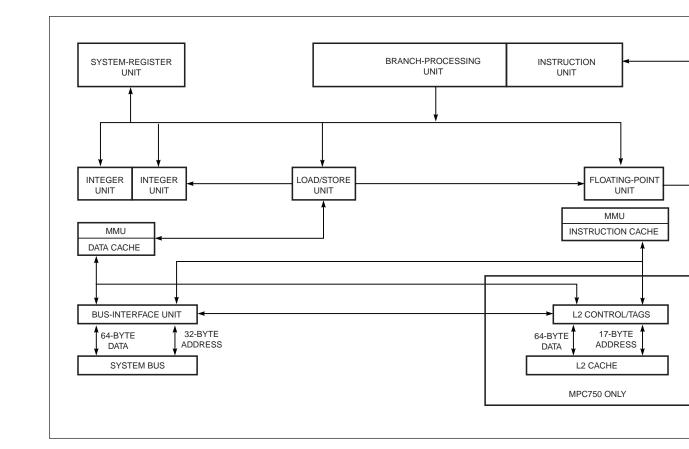

# **IBM/Motorola PowerPC**

Serving as a base for a family of RISC chips, the PowerPC derives its core architecture from the performance-optimized-with-enhanced-RISC (POWER) architecture. The instruction set and 32 32-bit, general-purpose registers support multiple microarchitecture implementations that include the 32-bit 603e, 604e, 740, 750, and embedded processors (Motorola's MPC 50x, MPC8x0, MPC82x, and IBM's 400 series).

The PowerPC 750 contains seven parallel-operating execution units: two integer units, a branch-processing unit, a load/store unit (LSU), a floating-point unit (FPU), a condition-register unit, and an L2-cache-interface unit. (The 740 is the lower cost version of the 750 and lacks the L2-cache-interface unit.) This CPU can fetch as many as four instructions per cycle. The 750 processes branches as they enter the instruction buffer and can decode and dispatch two nonbranches in one cycle. Completion logic keeps track of the outstanding instructions and retires them in order.

The PowerPC 750 mP uses static or dynamic branch prediction to improve the accuracy of instruction prefetching. For static prediction, the branch-operation codes provide hints to predict whether a branch is taken or not. For dynamic prediction, the CPU uses a 512-entry branch-history table and a 64-entry branch-target instruction. The CPU permits speculative execution down a predicted path beyond one unresolved branch.

The 750 has separate 32-kbyte instruction and data caches. Both eight-way, set-associative, lockable caches provide bytelevel parity checking. A locked cache typically supplies data on a hit, but cache lines are not replaced on a miss. The 750 contains an on-chip L2-cache controller and backside L2 bus, which improves system performance by reducing system-bus traffic. The L2-cache controller includes 8196 tag entries, which support 256 kbytes, 512 kbytes, or 1 Mbyte of external, two-way, set-associative, unified L2 cache. The L2 cache uses standard, commodity SRAMs. The nonblocking L2 cache supports hit-under-miss mode and can simultaneously service as many as four requests. The L2-cache bus can operate at various speeds relative to the processor frequency.

The PowerPC 604e contains seven independent execution units: two single-cycle integer units, a multiple-cycle integer unit, a branch-processing unit, an LSU, an FPU, and a condition-register unit. Instructions execute out of order, and execution results can be immediately available to subsequent instructions through the use of rename registers. The completion unit commits, or "retires," results to floating-point or general-purpose registers. The unit retires as many as four instructions per clock cycle in order, ensuring a precise exception model.

The PowerPC 604e mP uses dynamic branch prediction to improve the accuracy of instruction prefetching. This feature and the ability to speculatively execute through two unresolved branches minimize pipeline stalls. The 604e has separate 32-kbyte, four-way, set-associative instruction and data caches, both of which provide byte-level parity checking. *(continued on pg 142)*

## IBM/Motorola PowerPC (continued)

The 604e and 750 have separate memory-management units (MMUs) for instructions and data. The MMUs support as many as 4 petabytes of virtual memory and 4 Gbytes of physical memory. Access privileges and memory protection are controlled on 128-kbyte to 256-Mbyte blocks and 4-kbyte pages. Translation-look-aside buffers (TLBs) with 128 entries efficiently translate addresses by storing the most recently used page translations.

The 604e and 750 support 64-bit data and 32-bit address buses. The interface protocol allows multiple masters to access system resources through a central arbiter. The Power-PC 604e works in multiprocessor systems and snooping tasks and requires no additional bus cycles. The 604e's on-chip snooping logic maintains cache coherency in multiprocessor systems. The 750 supports snooping but is optimized for uniprocessor systems. It supports no data sharing among caches in different processors. The buses on the 604e and 750 are compatible electrically and in the protocol they use. A common chip set supports both processors.

The 603e comprises five parallel execution units: integer execution, floating point, branch, system, and load/store. With a four-stage pipeline—fetch, dispatch, execute, and complete—the 603 can achieve three instructions per clock cycle. During the fetch stage, the 603 uses a six-instruction prefetch queue to hold pending instructions. Unlike other PowerPC derivatives, the 603 supports only static branch pre-

diction. However, the architecture supports out-of-order execution and in-order retirement, similar to other PowerPC devices.

The embedded PowerPC processors include IBM's 400 series and Motorola's MPC500 and MCP800 families and devices. Compared with other PowerPC devices, these devices have similar-but fewer-execution units. IBM's 403Gx embedded controllers have a five-stage pipeline and can dispatch as many as two instructions per cycle. These devices implement static branch prediction and branch folding and have a four-instruction prefetch queue. Integrated caches of varying sizes are two-way set-associative and are implemented as fetch-through instruction caches and writeback data caches. (The 403GCX data cache does not provide write-through operation.) The 403Gx processors do not provide hardware support for maintaining cache coherency during DMA and external bus-master operations or in a multiprocessor configuration.

The PowerPC 403GC and 403GCX include an MMU featuring a fully associative TLB. Each entry provides translation for a memory page, which can be one of several sizes for efficient system-memory use. Memory components attach directly to the 403 devices with a programmable-memory interface on the processor's bus-interface unit. The DRAM controller includes the address multiplexer, eliminating the need for an external address multiplexer. The DRAM con-

## IBM/Motorola PowerPC (continued)

troller supports external bus masters. You can use software with external memories, other CPUs, and peripherals. The SIU for the MPC505 and MPC509 differs from the one in the programming to tune the timing for the interface control signals. 800 family devices and in the MPC555. The 505 and 509 SIUs The PowerPC 401GF implements a three-stage pipeline have separate data and instruction buses; the 800 and 555 and supports hardware multiply and divide and unaligned devices combine these buses outside the SIU. The 800 family loads and stores. The CPU uses operand forwarding and stahas both instruction and data caches and an MMU. The tic branch prediction to increase performance. The 401GF's caches are two-way set-associative and feature lockability on cache controllers implement critical data forwarding, filla line.

first handling of cache misses, and nonblocking flush operations.

Motorola's MPC500 and MPC800 families, although targeting different applications, have the same basic CPU architecture. (However, the new MPC8260 PowerQUICC II is an upgrade of the MPC860 and contains a PowerPC EC603e core.) Both families integrate a fixed-point unit (FXU), an LSU, two register files, and a sequencer unit; the MPC500 family also adds an FPU. The FPU includes single- and double-precision multiply-add instructions. The sequencer unit contains a branch processor featuring static branch prediction and branch-folding capability during execution (zerocycle branch execution time) and runtime reordering of loads and stores.

The MPC500 and MPC800 devices use an InterModule Bus, developed for Motorola's 683xx devices, as a backplane real-time, noninvasive trace capability. to connect all system modules. Both families include a sys-Second sources: Mitsubishi is a second source for IBM's tem-integration unit (SIU) that enables simple integration embedded PowerPC mPs.

Special instructions: Motorola has expanded the PowerPC architecture with its AltiVec technology-162 new instructions along with a 128-bit vector-execution unit that performs single-instruction multiple-data operations concurrently with the integer units and FPUs. AltiVec supports 16-way parallelism for 8-bit integers and characters, eightway parallelism for 16-bit integers, and four-way parallelism for 32-bit integers and IEEE floating-point numbers. AltiVec also includes a separate register file with 32 128-bit-wide registers.

**Development tools:** The PowerPC families have a large third-party tool-supplier base. IBM also offers development tools for all its PowerPC embedded processors. These tools include a C/C++ compiler; a RISCWatch debugger with in-circuit emulation; a ROM monitor; RTOS-aware debugging; and

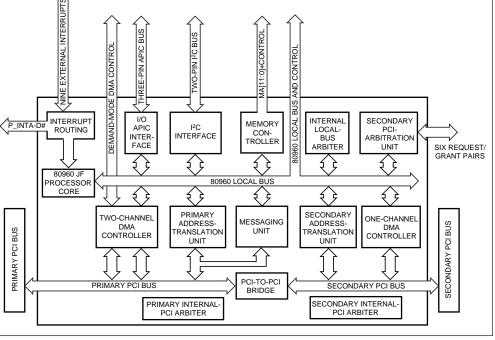

## Intel i960

The range of i960s runs from the new superscalar HA/HD/HT to the 16-bit SA/SB variants, including low-power versions of the i960 Jx series that operate at 3.3V. The i960 combines a von Neumann architecture with a load/store architecture that centers on a core of 32 32-bit general-purpose registers comprising 16 local and 16 global registers. An on-chip register cache automatically caches the local register sets to speed context switching. If the cache is full, the oldest cached set moves to memory, and the latest set caches. All i960s have multistage pipelines and use resource "scoreboarding" to track resource usage.

The i960CA provides superscalar operation and five pipeline stages. The key to the Cx is its four-instruction-wide in-

struction decoder, which decodes as many as four instructions per cycle. Current implementations dispatch as many as three of these instructions for execution. The i960CF has 128-bit-wide buses to move instructions to the decoder and 128-bit-wide buses to move data between the cache and registers.

Intel built the superscalar i960s around a six-port register file with register or memory-control execution units. These units include an integer unit, a floating-point unit, and an interrupt-control unit on the register side and address-generation and bus-controller units on the memory side. The i960s can cache instructions in a lockable cache; later versions add an instruction cache to supplement the register cache.

Intel based the i960Rx series I/O processors on the i960 Jx series processor core. The i960Rx processors target servermotherboard and adapter-card applications, in which the processors create an "intelligent" I/O subsystem. Intel and others have developed an intelligent I/O (I<sup>2</sup>O) specification to speed I/O processing and simplify driver development. Special instructions: The i960 family has uninterruptible atomic add and modify instructions. Other instructions flush local registers and provide cache-locking control. Development tools: More than 70 vendors support the i960

with a robust tool suite. These vendors offer a range of compilers, emulators, evaluation boards, debugging monitors, and real-time operating systems for the i960 family.

# MIPS R3000

MIPS (www.mips.com) built the MIPS R3000 processors as large as 40%. LSI Logic, with its TinyRISC TR4101, is the around a set of 32-bit, general-purpose registers in a central register file. To minimize control logic and improve speed, the instruction set has only 73 instructions, and addressing options are few. The chip has a three-address load/store architecture. Similarly, instructions are one 32-bit word to minimize decoding and speed processing. To reduce code size, MIPS and LSI Logic codesigned the MIPS16 application-specific extension. MIPS16 comprises new 16-bit instructions with a corresponding decoding block that the MIPS mP core integrates. Although most applications still need to run 32bit code (MIPS16 supports a mixture of 32- and 16-bit code), MIPS claims that MIPS16 provides an overall memory savings

first MIPS licensee to implement the MIPS16 instruction extensions

MIPS engineers implemented a five-stage pipeline: instruction fetch, read operand and decode instruction, execute, access data memory, and write back results for the R3000. The pipeline lets as many as five instructions execute concurrently—each at a different stage of its instruction cycle. A branchdelay slot minimizes branch effects. The compiler fills the instruction slot, following the branch with a no-operation instruction or an instruction from the current thread that can execute before the branch takes effect. Toshiba's R3900 and Integrated Device Technology's (IDT) RISCore32300, R3000

derivatives, incorporate register "scoreboarding" to enable nonblocking loads and avoid pipeline stalls when there are no data dependencies in subsequent instructions. This feature has a significant benefit in communications applications: It allows programmers to hide main-memory latencies during routing or packet processing. On IDT's 32300, you can also use the nonblocking load for cache prefetch and for performing DMA transfers without performing invalidates and write-backs. IDT implemented this feature as a new hint, called "ignore hint." This feature helps you get around the MIPS instruction-set architecture's lack of "move-multiple" operations. The 32300 also supports a mechanism to minimize pipeline stalls; in the event of a cache miss, the first entering word goes directly to the pipeline.

To improve the multiply and divide performance of the standard R3000, IDT built in a dedicated integer multiply/ divide unit. In the MIPS instruction-set architecture, multiply and divide use special destination registers, permitting only one multiply at a time. IDT enhances this capability with a three-operand multiply, whereby the operand results go directly to a general register. This feature supports DSP capability and performs atomic multiply adds and multiply subtracts. It also implements count-leading ones and zeros operations. The multiply-add throughput is one cycle faster than the data latency, so if you use two distinct operands, the operation becomes load-bound. Whereas the general MIPS mechanism supports reset, cache/parity error, user translation-look-aside-buffer (TLB) miss, and general interrupts, IDT's 32300 lets you define separate interrupts to support software compatibility with your legacy code.

The standard R3000 memory-management unit includes a fully associative, 64-entry TLB that translates virtual addresses to 32-bit physical addresses. (Note: Not all R3000 derivatives contain the TLB.) The mP uses a write-through cache policy. A small on-chip FIFO buffer enables the CPU to perform instruction "streaming"-refilling the cache and executing instructions even while reading additional instructions from

IDT's 33-MHz 79S381 evaluation board allows you to evalmemory. Special instructions: The R3000 implements the MIPS-I uate the 3041, 3052, and 3081 mPs. The board features 2 instruction set. IDT's 32300 uses the MIPS II instruction-set Mbytes of interleaved DRAM, expandable to 16 Mbytes; 256 architecture but includes some MIPS-IV functions. It implekbytes of zero-wait-state SRAM: 512 kbytes of EPROM. ments those MIPS-IV instructions, such as prefetch operaexpandable to 2 Mbytes; and a 1024-bit serial EEPROM. The tions and conditional moves, that are independent of company provides the 79S361 evaluation platform for the operand size. The 32300 also supports both big- and little-79R36100. This board has 1 Mbyte of noninterleaved, zeroendian data types. Several of the MIPS derivatives add a mulwait-state DRAM, expandable to 64 Mbytes. It also contains tiply-accumulate (MAC) instruction. LSI is the first MIPS 2 Mbytes of EPROM and a slot for 1 Mbyte of zero-wait-state licensee to implement MIPS16 instruction extensions on the SRAM. TinyRISC TR4101. Toshiba's TX19 also uses the MIPS16 IDT offers its kernel-integration tool that includes sourceinstruction extensions. (See R4xxx, pg 169, for more details.) and object-code versions of common routines for CPU Special on-chip peripherals: Philips offers the TwoChipPIC. design. The company also offers a system-integration moniwhich combines the UCB1200 that interfaces with the comtor that is a ROMable debugging kernel. The monitor pany's PR31700 MIPS mP. The TwoChipPIC provides a includes IDT's micromonitor, which requires only a UART microsystem on a chip for handheld devices. Integrated modand ROM to perform the initial debugging and integration of ules include a MAC unit, an LCD controller, an infrared connew hardware. IDT/C is an ANSI C-compliant Gnu compiler, troller, PCMCIA-card support, touchscreen control, and assembler, linker, and librarian. It includes start-up code, audio in/out. Toshiba's peripherals include a graphics concache, and exception routines. troller, a PCI controller, and support for Microsoft's Toshiba offers evaluation boards for its TX39 products. (www.microsoft.com)Windows CE.

Development tools: A range of third-party development tools is available for the MIPS RISC architecture. Detailed VxWorks and Tornado RTOS support these boards. Toshiba information is available in the MIPS RISC Resource Catalog also offers the TMPR3912 and TMPR3922 reference development systems that support the Microsoft Window CE operfrom MIPS Technologies Inc or at www.mips.com. Philips supplies the hardware-abstraction layer, device drivers, a refating system. erence design, and a development board for Windows CE Second sources: MIPS licenses the R3xxx processors to IDT, implementation on the TwoChipPIC. Microsoft's Visual C++ LSI Logic, NKK, Philips, and Toshiba.

tool chain supports TwoChipPIC development.

LSI Logic offers evaluation boards and kits for its line of TinyRISC and MiniRISC mPs and cores. For example, the company's BDMR4101 evaluation board uses an 81-MHz TR4101 CPU core and features 1 Mbyte of SRAM and an 8-Mbyte plug-in DRAM single-inline-memory module, 512 kbytes of flash, a full-duplex serial port, SCN2681 dual UART with dual RS-232C ports, the DP83934 Sonic Ethernet controller with a 10BaseT interface, and the SerialICE debugging monitor and software in EPROM. It supports both PC and Unix host environments. LSI offers a number of tools, including the Mini-SIM and TinySIM architectural simulators for system-on-chip embedded applications, as well as a system-verification environment for silicon-design verification. LSI Logic also provides application-specific evaluation boards, such as the Integra for set-top-box development and the ATMIzer II for communication-product development.

These boards feature support for serial, SCSI-II, Ethernet, or VMEbus interfaces. Wind River's (www.windriver.com)

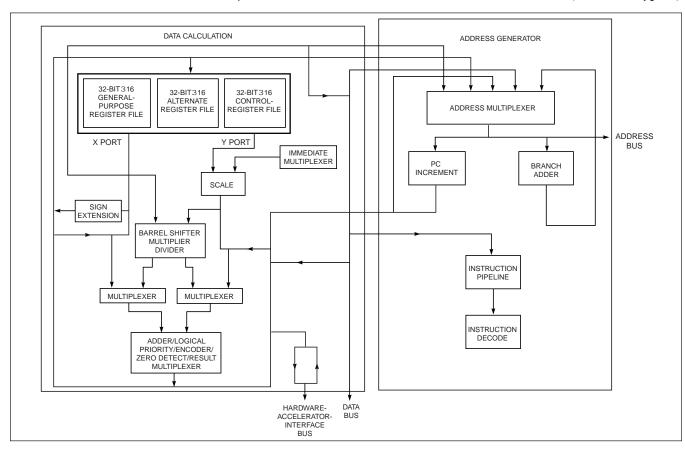

# Mitsubishi M32Rx/D

The Mitsubishi M32Rx/D contains a 32-bit RISC CPU; as much as 4 Mbytes of on-chip DRAM, which Mitsubishi calls "eRAM"; a 32316-bit multiply-accumulate (MAC) unit; and a bus-interface unit (BIU). A 128-bit, 66-MHz internal bus connects the CPU, DRAM, cache, and BIU. The M32Rx/D's circuitry automatically refreshes the internal DRAM.

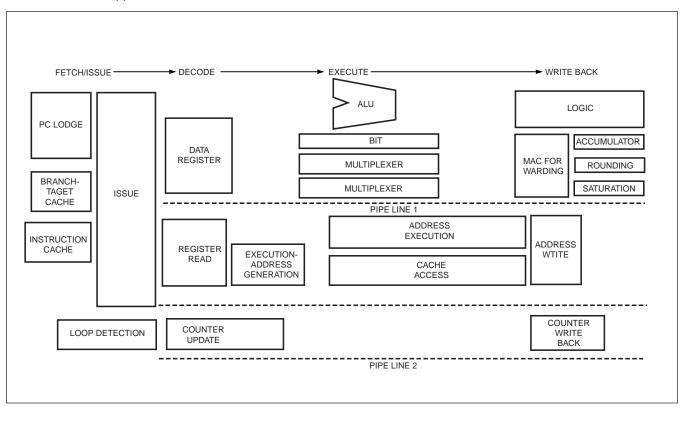

The M32Rx/D family comprises the M32R/D and the new superscalar M32Rx/D architectures. Both architectures are instruction-set-compatible and comprise a combination of 16- and 32-bit-wide instruction formats with six addressing modes. The devices include 16 32-bit, general-purpose registers and two 56-bit accumulators.

The M32R/D CPU executes most instructions in one clock cycle, using an instruction-fetch, decode, execute, memory-access, and write-back pipeline. The decode stage dispatches instructions in order, and the remaining stages execute them out of order to hide memory-access latency. The MAC unit contains a single-cycle, 32316-bit multiplier and a 56-bit adder.

The M32Rx/D contains a dual-issue, six-stage pipeline and performs out-of-order execution; it can execute two 16-bit instructions in parallel. The pipelines are asymmetrical, and instructions have to align properly to keep the pipes full. For example, both pipelines can execute arithmetic and logical operations, but only Pipeline 1 can execute load/store and jump/branch instructions. Additionally, only Pipeline 2 can execute MAC instructions.

Both CPUs have an instruction queue of two 128-bit entries. The cache maps directly to the address space and has caching modes for internal instruction and data, for internal and external instructions, and for cache off. If a cache miss occurs, the CPU fetches one 128-bit data line in five cycles. The BIU has 128-bit data buffers and supports burst transfers on 128-bit boundary data.

A 16.67-MHz bus clock and four digital PLLs generate the internal 66-MHz clock. The PLL contains a digital frequency multiplier. Four cascaded, 64-tap inverter chains generate four timing edges in one-half of a clock cycle. A phase detector and an up/down counter adjust the pulse width to one-fourth of the one-half clock cycle to keep the duty cycle of

the four-times clock at 50%. The generated clock then feeds into a digital phase shifter to reduce the phase difference between the external and internal clocks to 400 psec.

**Power management:** The M32Rx/D supports sleep and standby modes, during which the average power consumption is 170 and 2 mW for the two modes, respectively, for the 2-Mbyte version. In the sleep mode, the CPU and caches stop; in standby mode, only the DRAM is clocked.

**Special instructions:** The M32Rx/D supports MACs of 32316 and 16316 bits. It also performs data rounding in the accumulator and block moves. The M32R/D and M32Rx/D support 83 and 95 instructions, respectively. The M32Rx/D's additional instructions include five DSP-function instructions for MAC and rounding operations.