Semester: IV Branch: Computer Science & Engineering Subject: Computer Systems Architecture Code: 322414 (22) Total Theory Periods: 40 Total Tut Periods: 10 Total Marks in End Semester Exam: 80 Maximum number of Class Tests to be conducted: 2

## **Unit 1: Processor Basics**

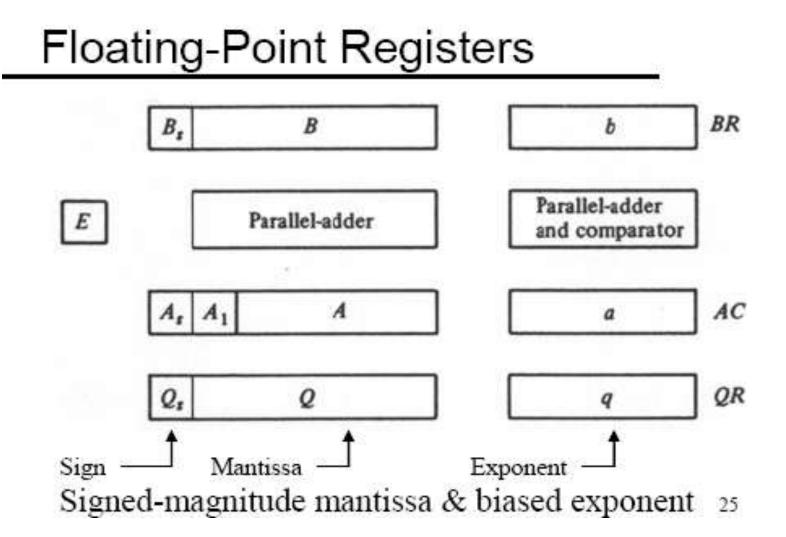

CPU Organization, Fundamental and features, Data Representation formats, Fixed and Floating

point representation, Instruction Sets, Formats, Types and Programming Considerations.

## **Unit 2: Datapath Design**

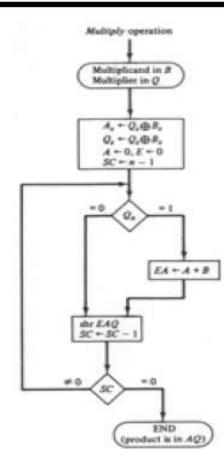

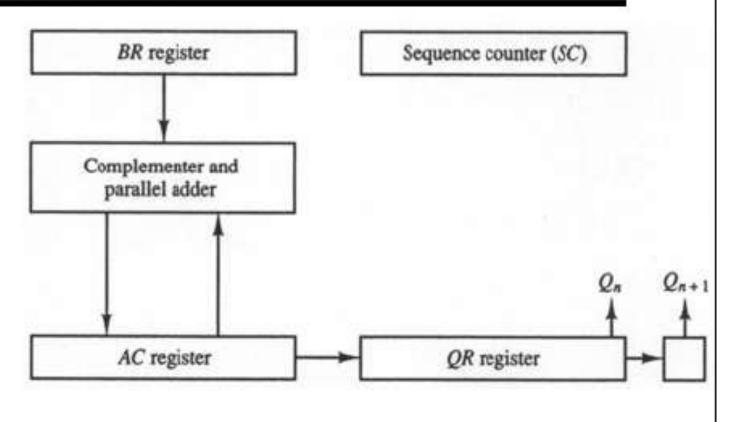

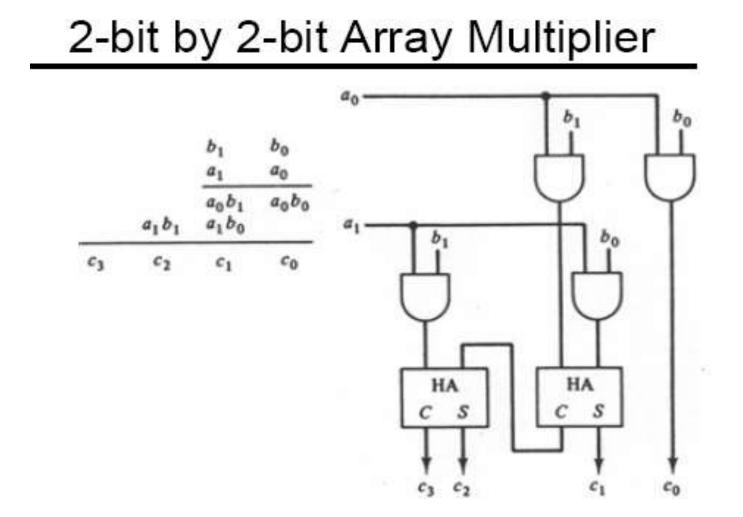

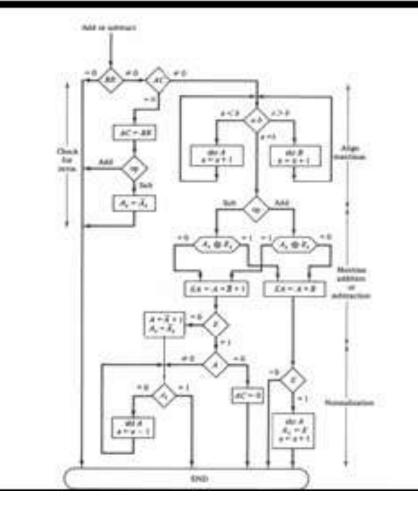

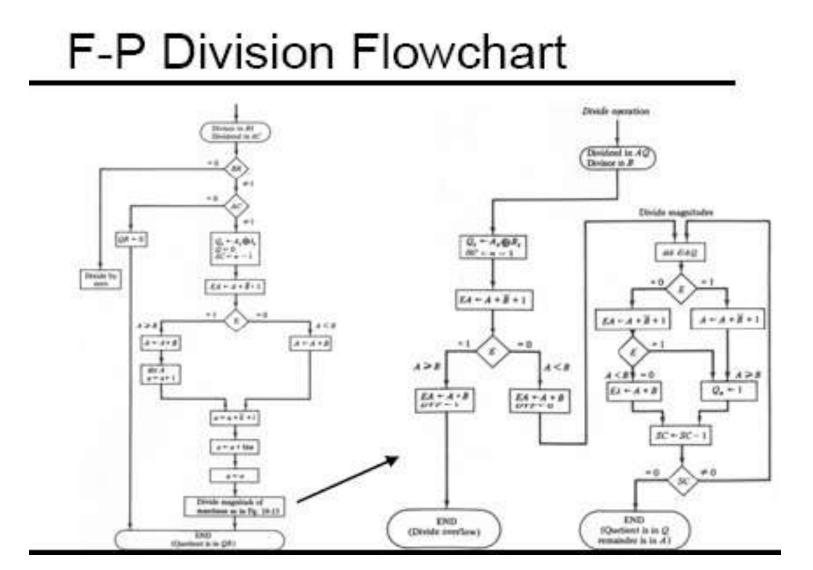

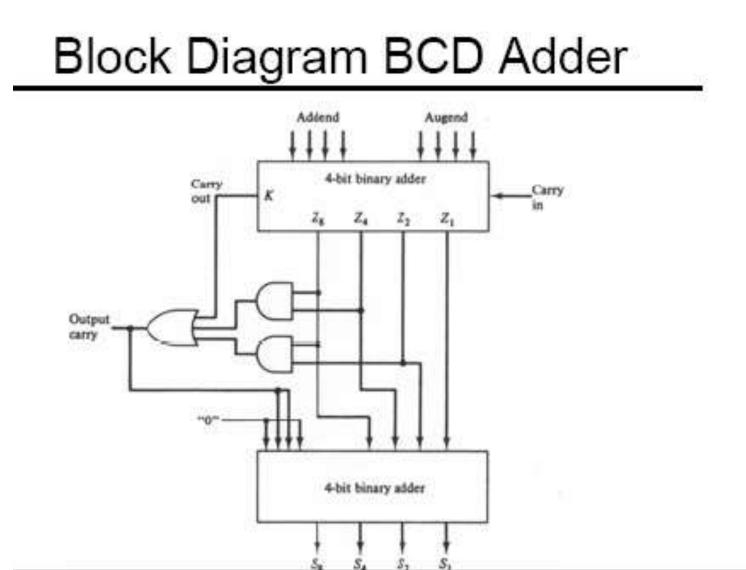

Fixed-Point Arithmetic, Combinational ALU and Sequential ALU, Floating point arithmetic and

Advanced topics, Hardware Algorithm – Multiplication, Division.

## **Unit 3: Control Design**

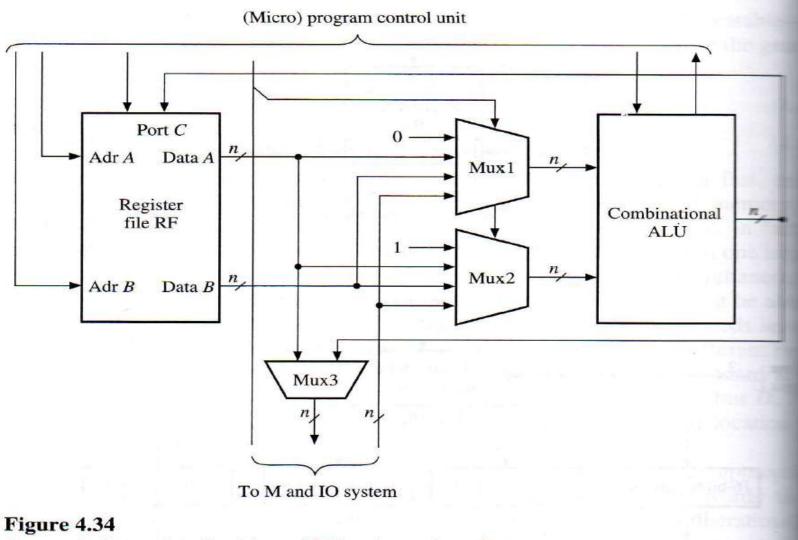

Basic Concepts, Hardwired control, Microprogrammed Control, CPU control unit and Multiplier

control unit, Pipeline Control.

## **Unit 4: Memory Organization**

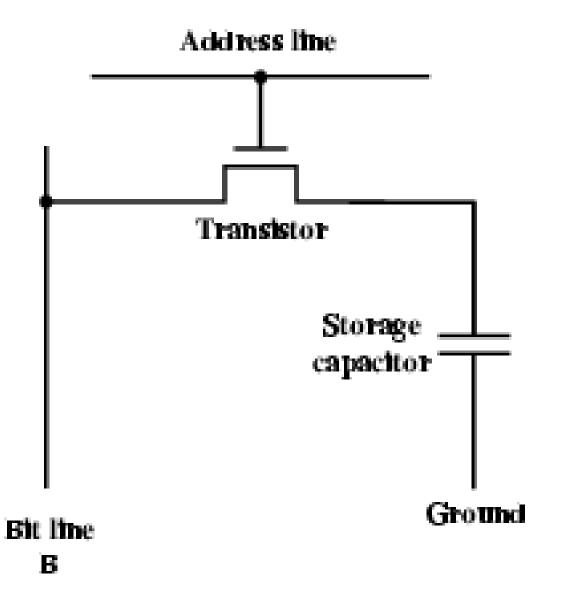

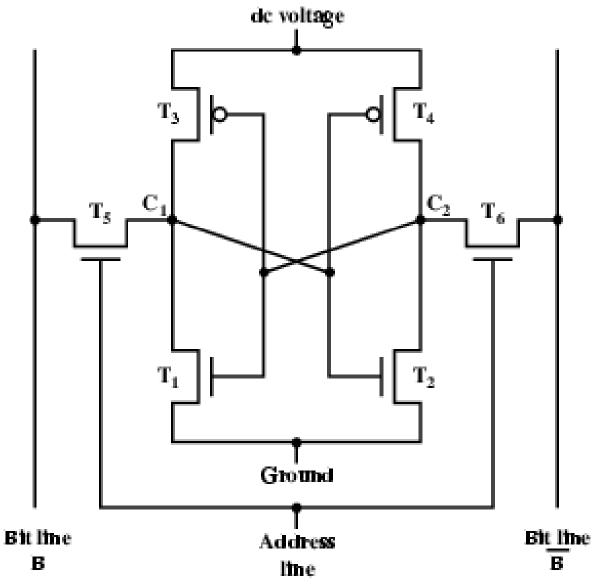

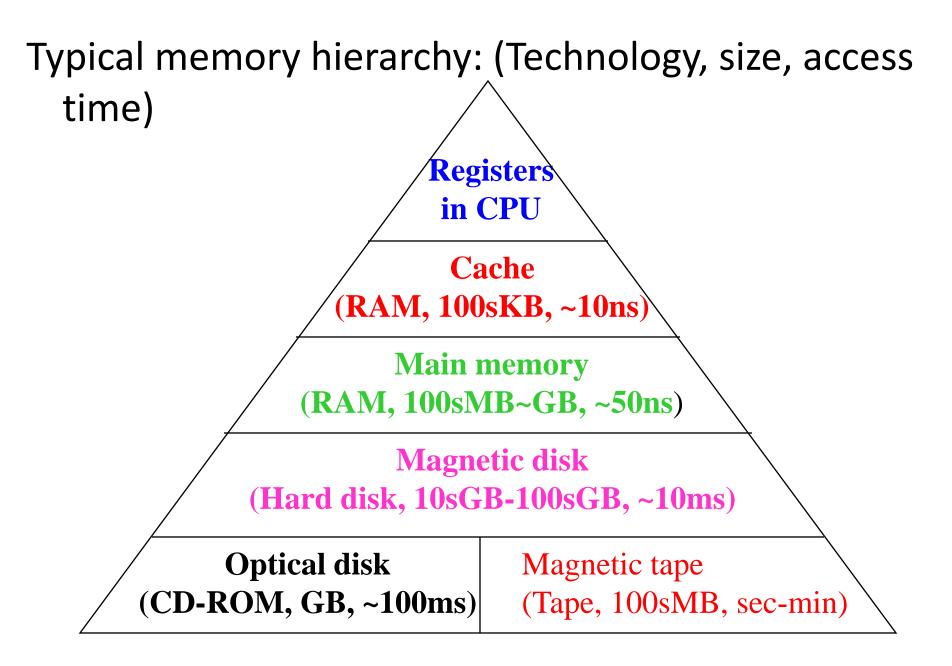

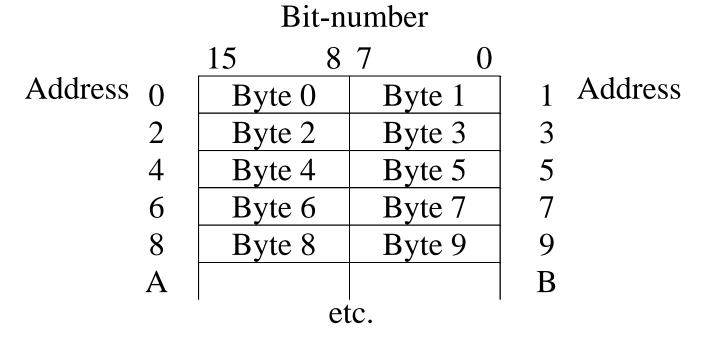

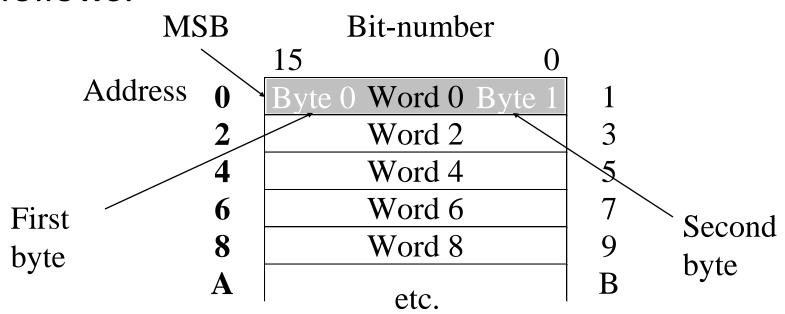

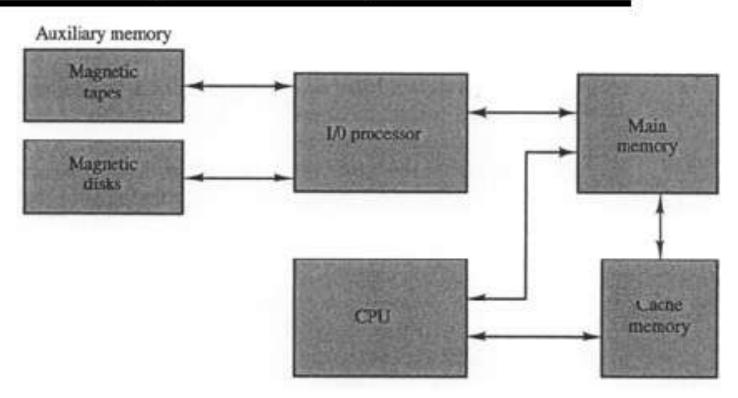

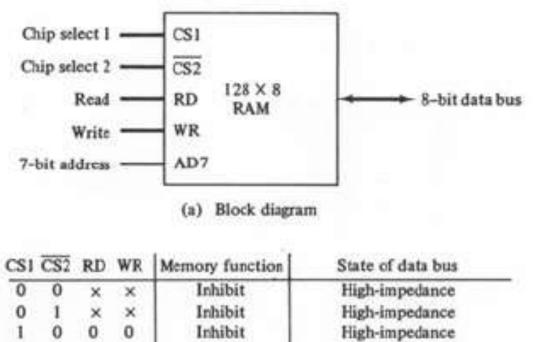

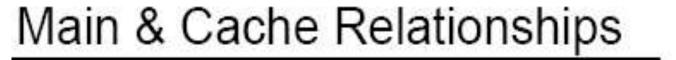

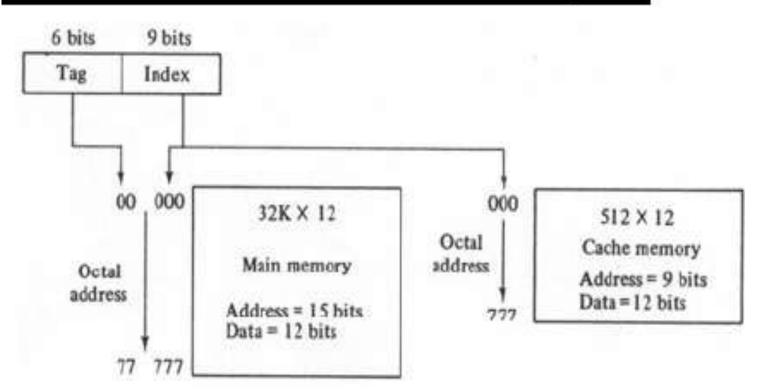

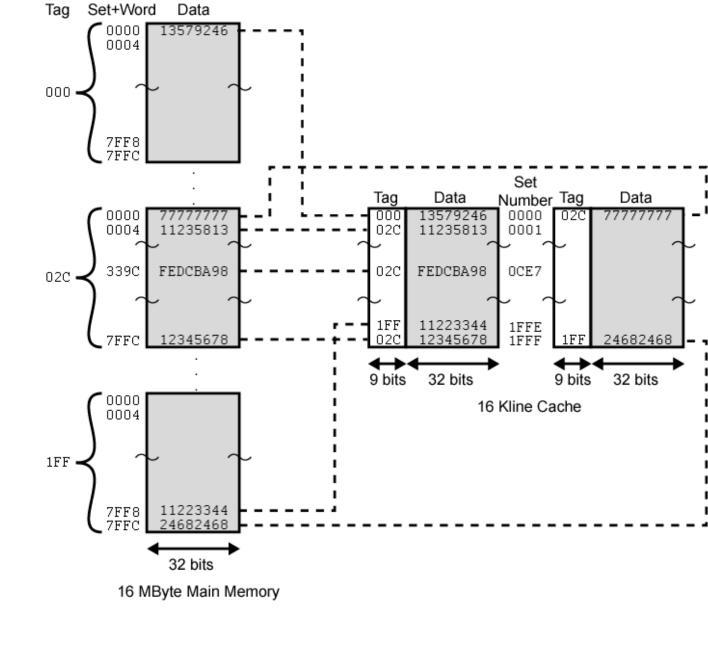

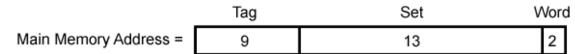

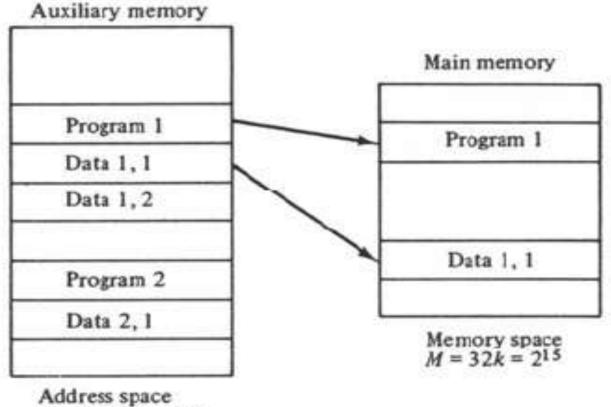

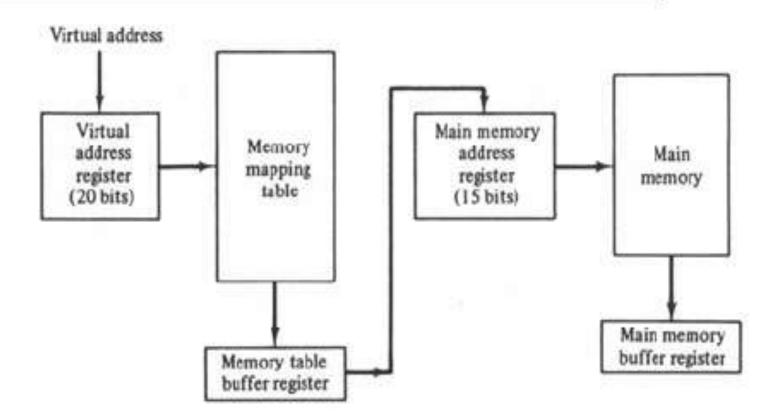

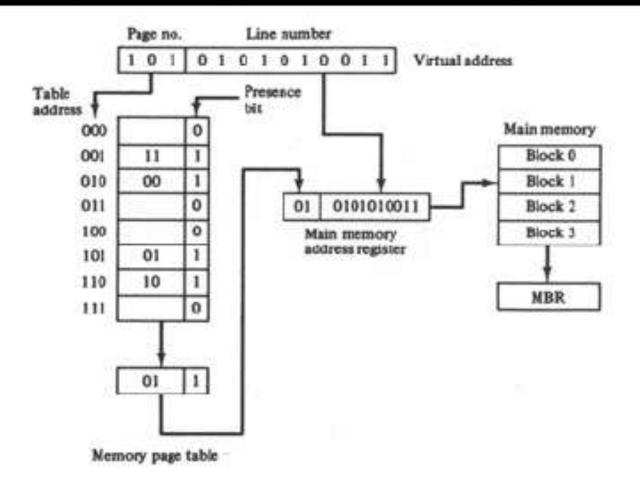

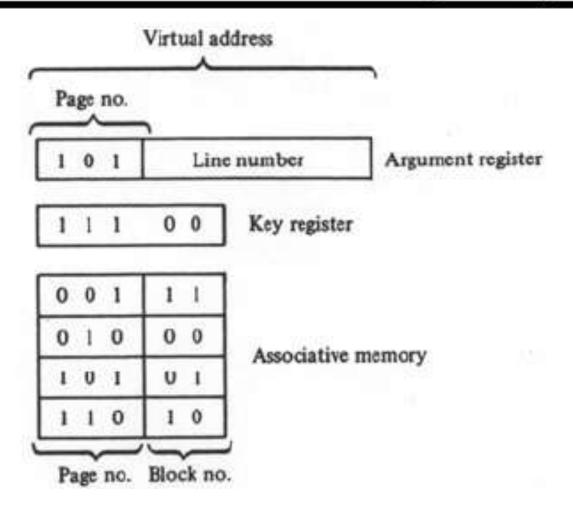

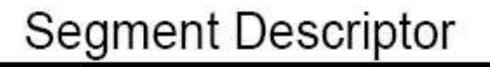

Memory device characteristics, RAM technology and Serial access memories technology,

Multilevel memory systems, Address translation and Memory allocation systems, Caches

memory.

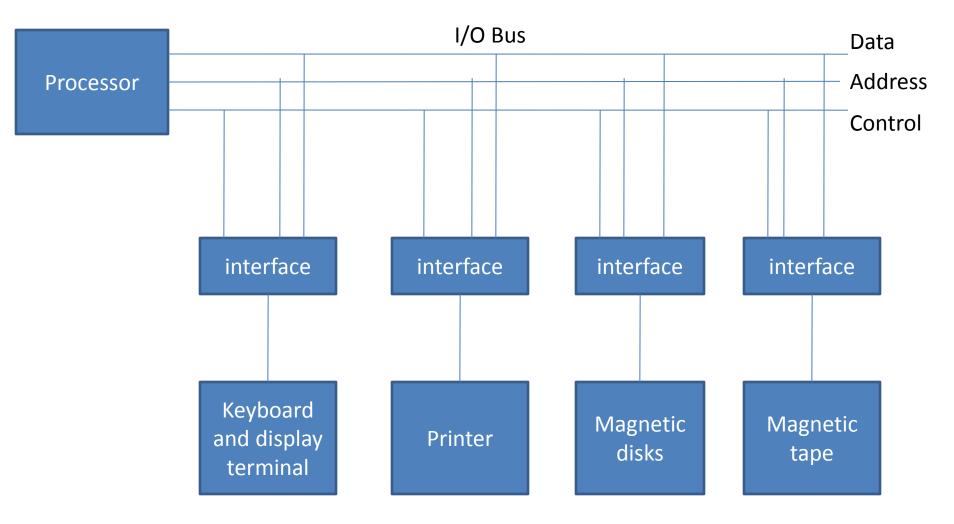

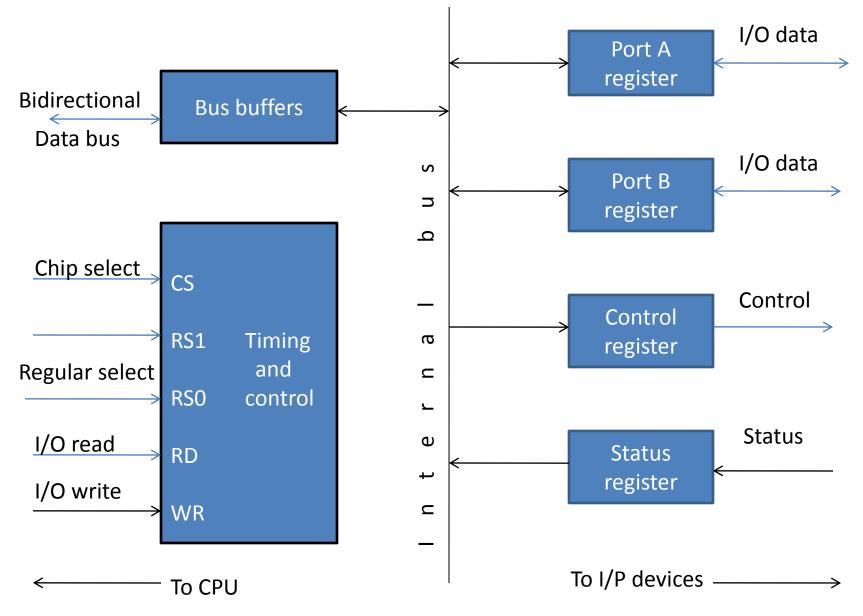

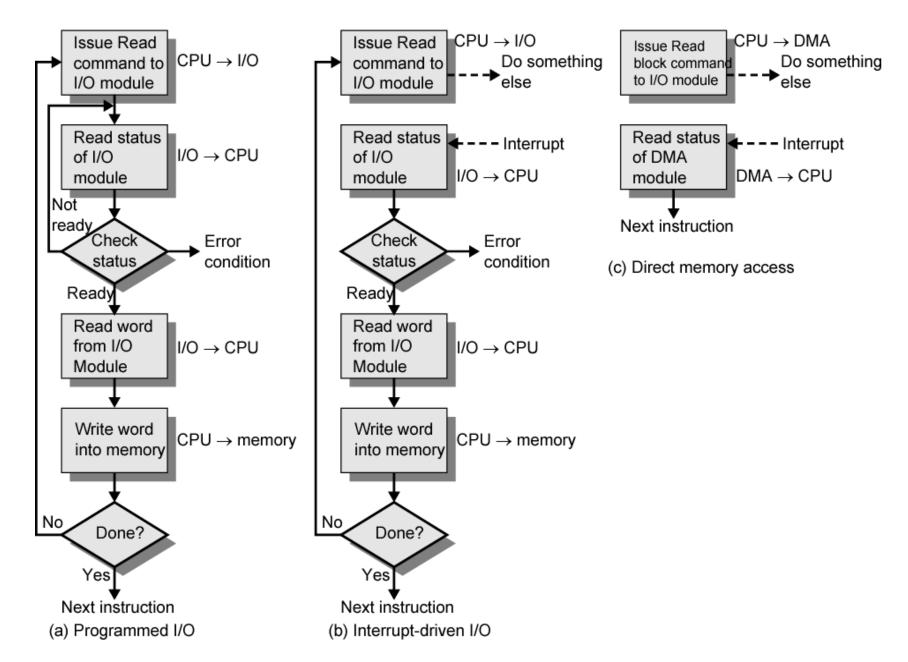

## **Unit 5: System Organization**

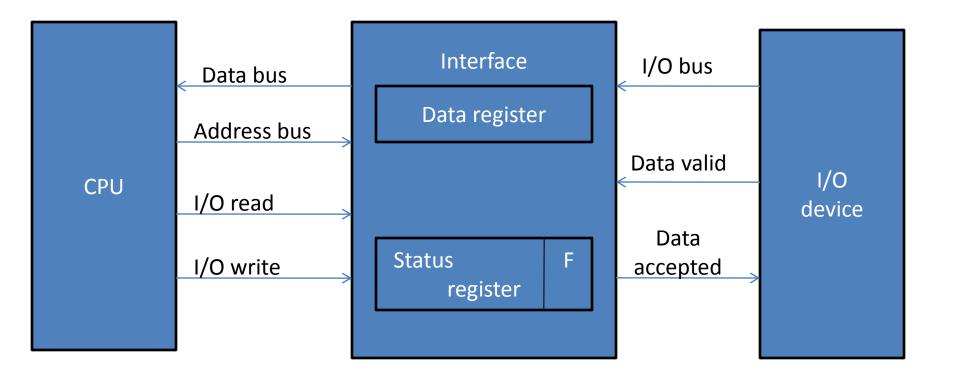

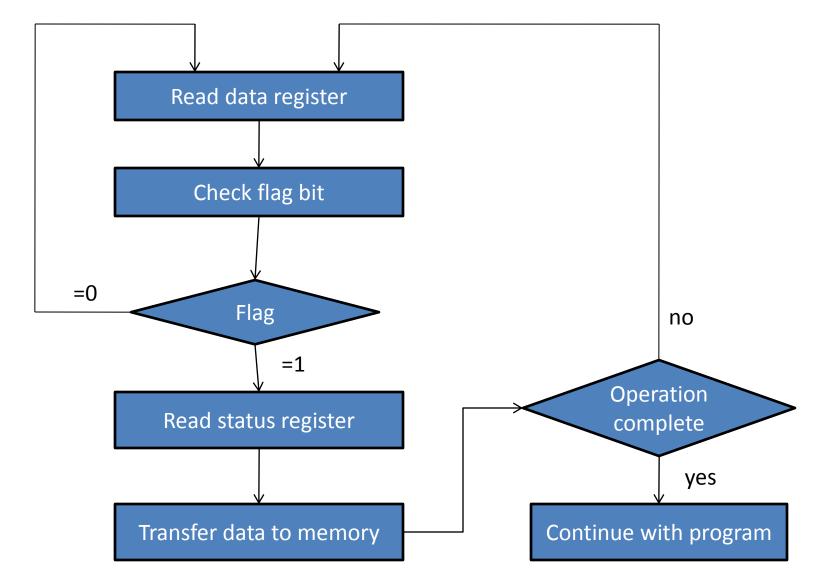

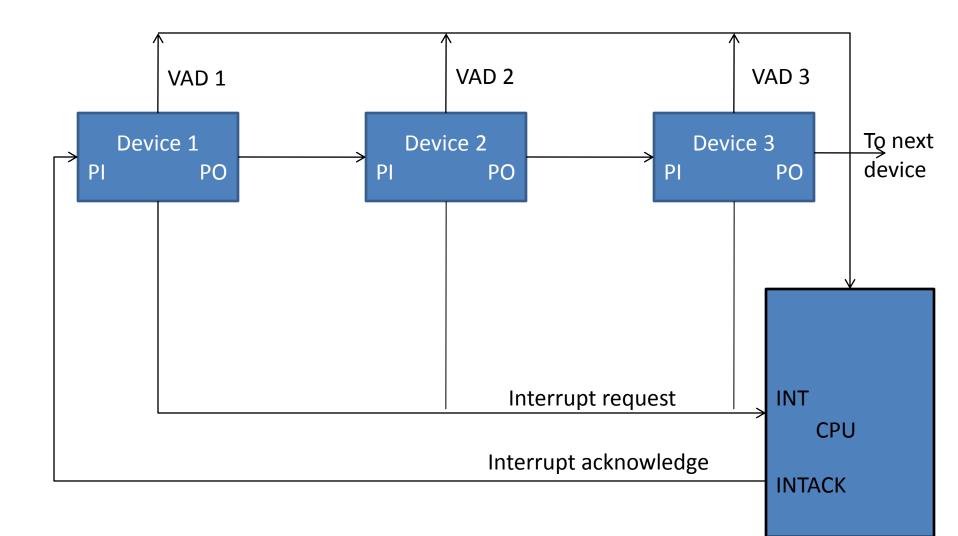

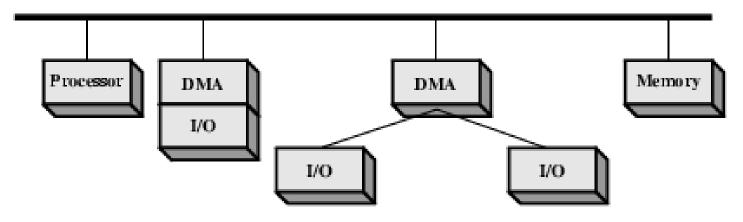

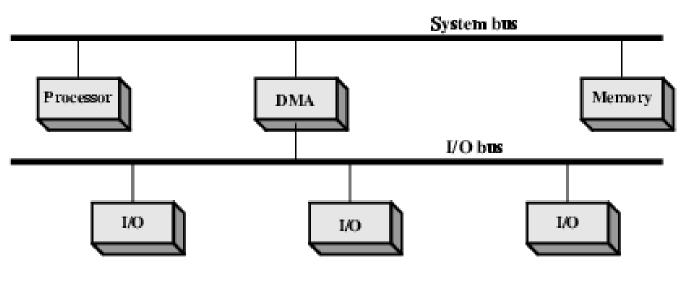

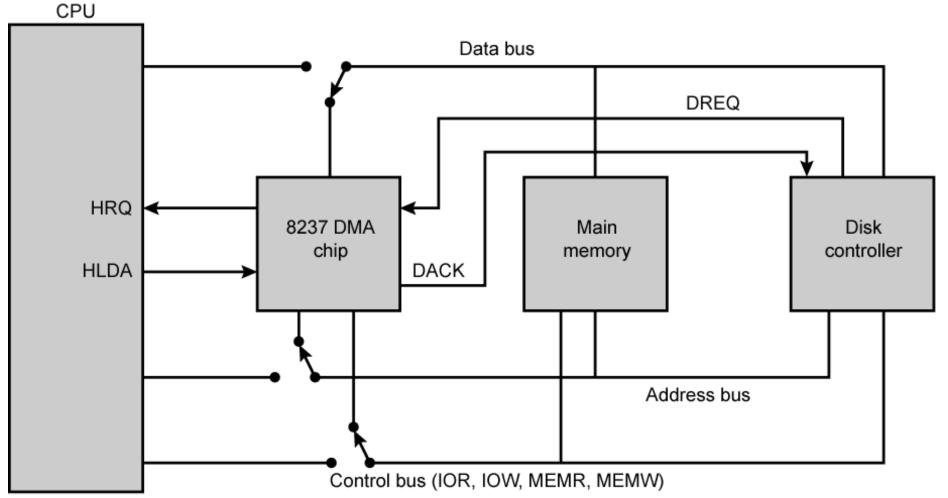

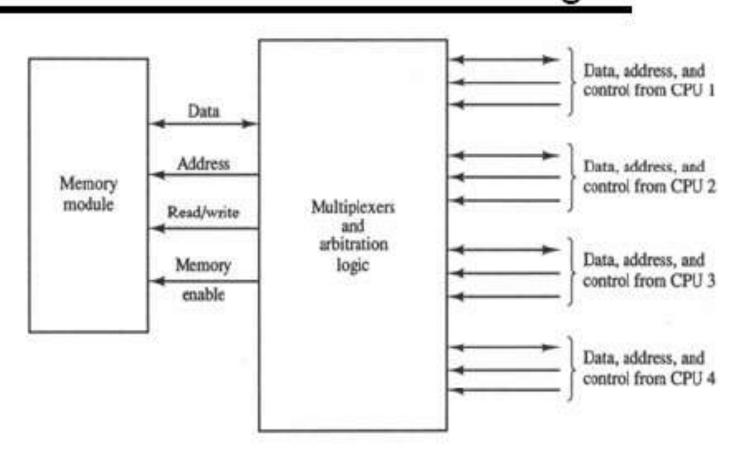

Programmed I/O, DMA, Interrupts and IO Processors, Processor-level Parallelism, Multiprocessor and Fault tolerance system.

## Name of Text Books

1. Computer Architecture and organization – John P Hayes, McGraw Hill Publication 2 Computer Organizations and Design- P. Pal Chaudhari, Prentice-Hall of India **Name of reference Books:**

1. Computer System Architecture - M. Morris Mano, PHI.

Computer Organization and Architecture- William Stallings, Prentice-Hall of India

Architecture of Computer Hardware and System Software: An Information Technology Approach,

3rd Edition (Illustrated) – Iry Englander, John Wiley & Sons Inc

4 Structured Computer Organization Andrew S Tanenbaum, Prentice-Hall of India

5 Computer Systems Organization & Architecture – John D Carpinelli, Addison-Wesle

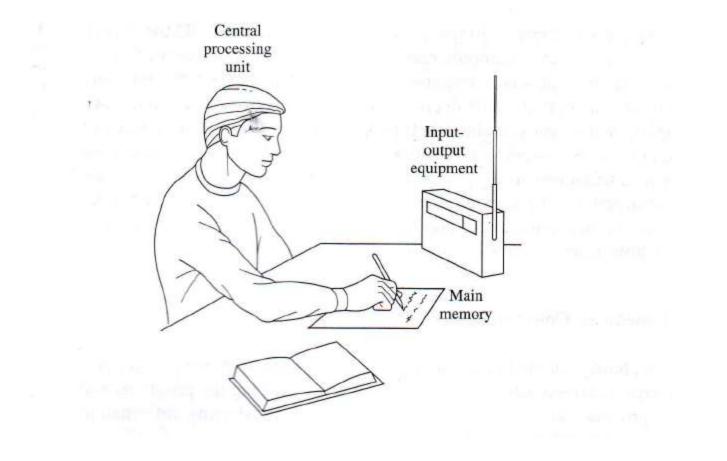

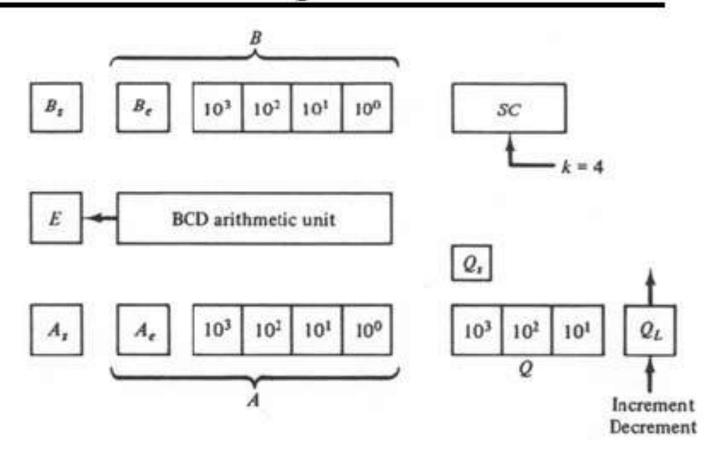

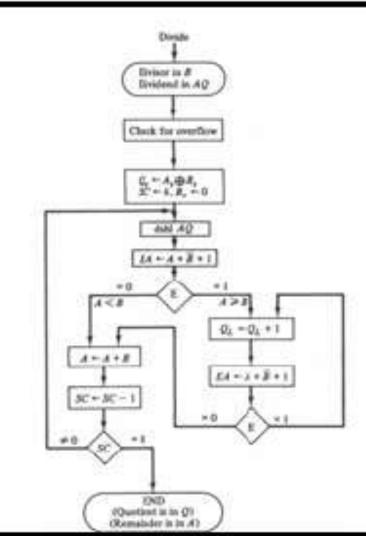

#### Figure 1.2

Main components of (a) human computation and (b) machine computation.

#### Figure 1.11

Organization of a first-generation computer.

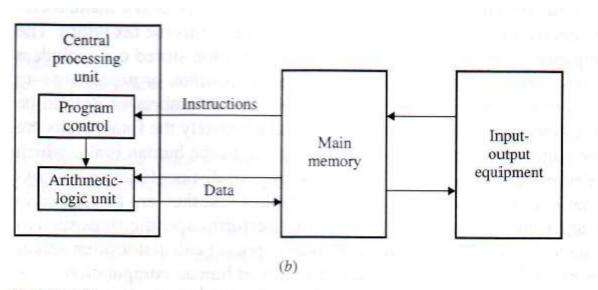

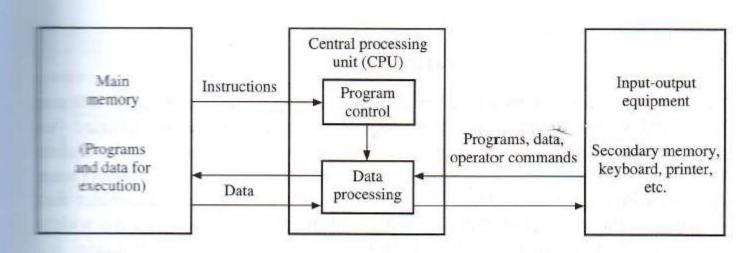

## CPU ORGANIZATION

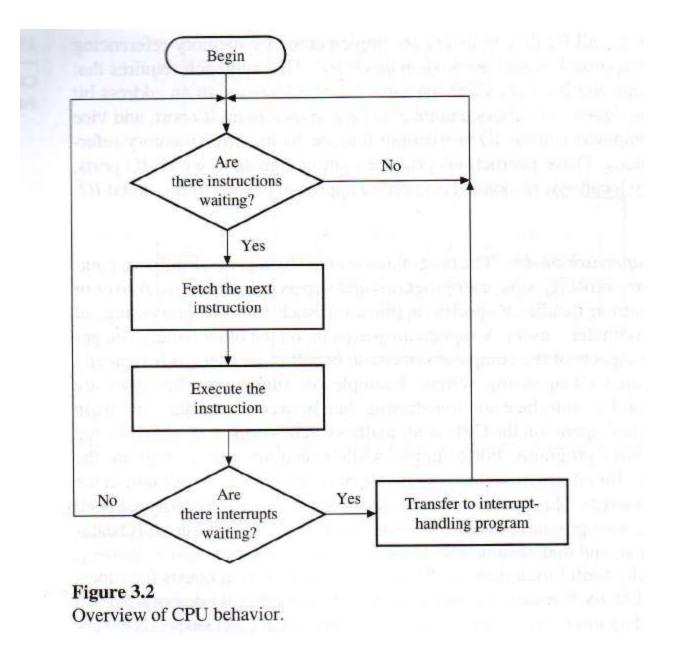

The primary function of the CPU and other instruction-set processors is to execute sequences of instructions, that is, programs, which are stored in an external main memory. Program execution is therefore carried out as follows:

- I The CPU transfers instructions and, when necessary, their input data (operands) from main memory to registers in the CPU.

- 2 The CPU executes the instructions in their stored sequence except when the execution sequence is explicitly altered by a branch instruction.

- When necessary, the CPU transfers output data (results) from the CPU registers to main memory.

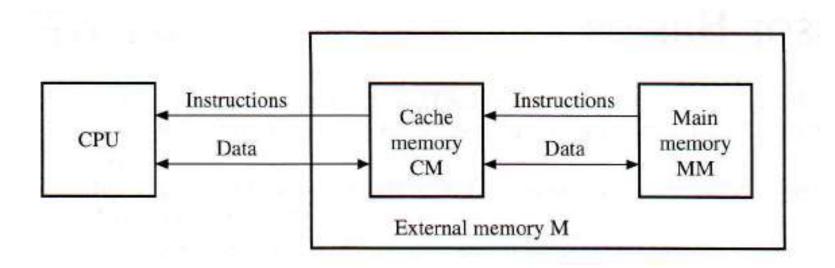

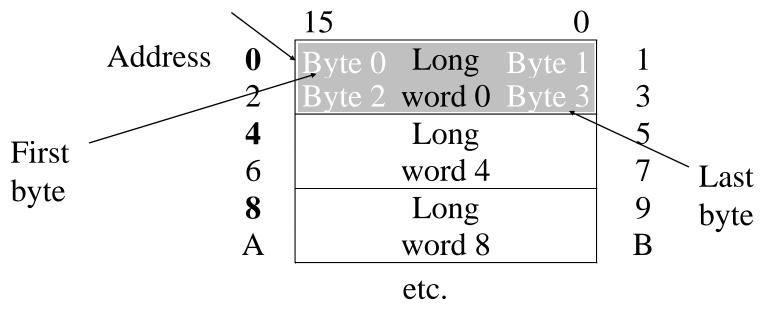

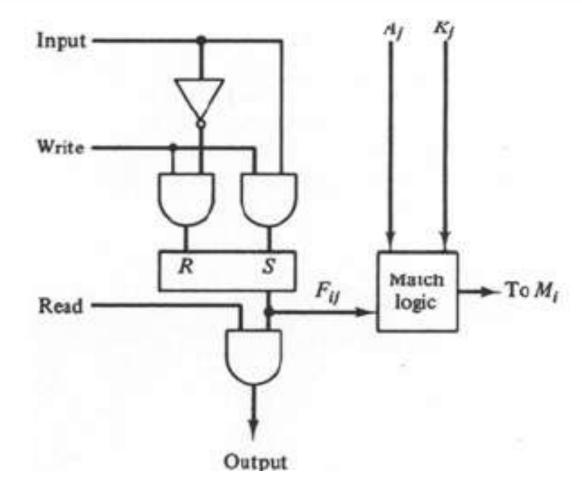

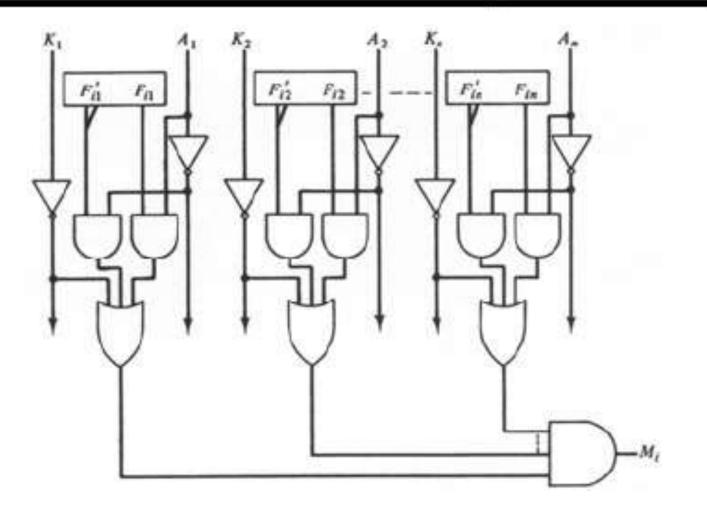

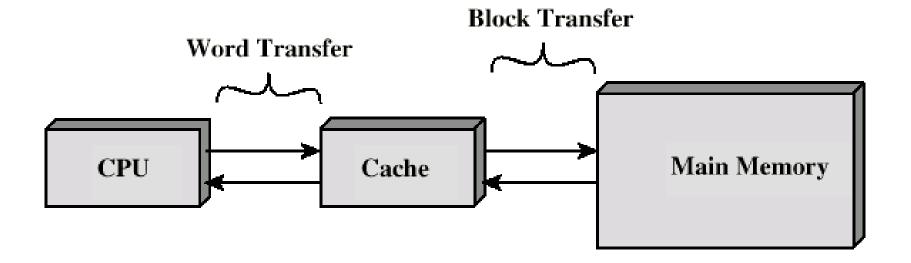

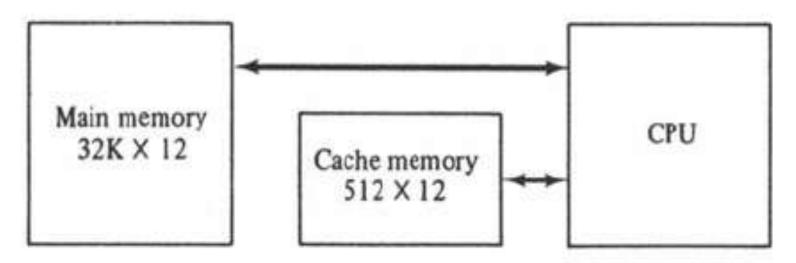

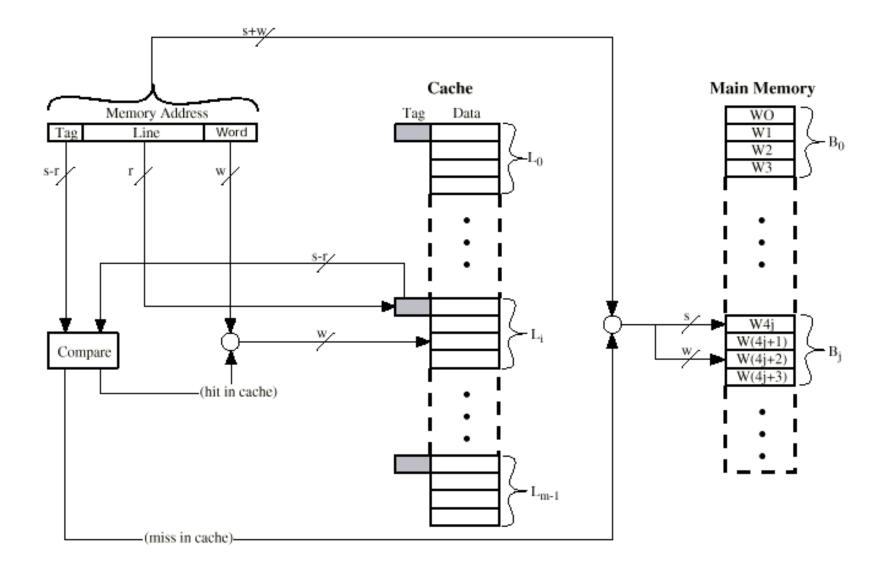

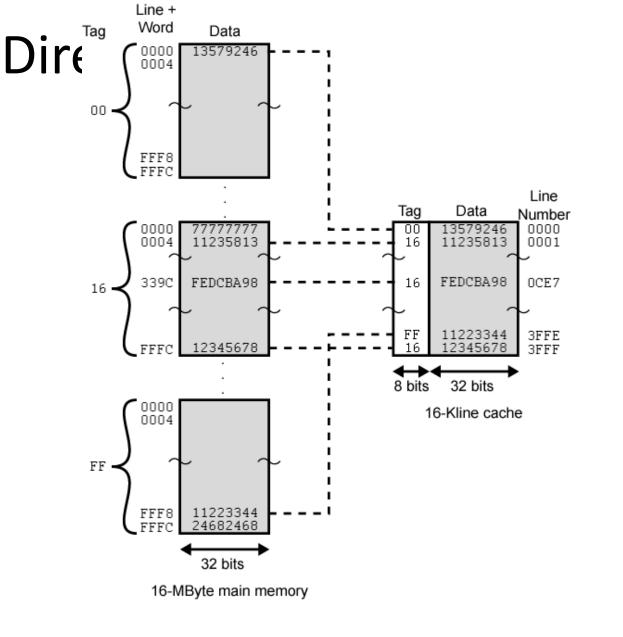

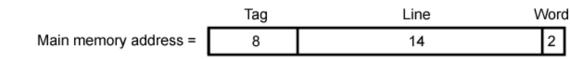

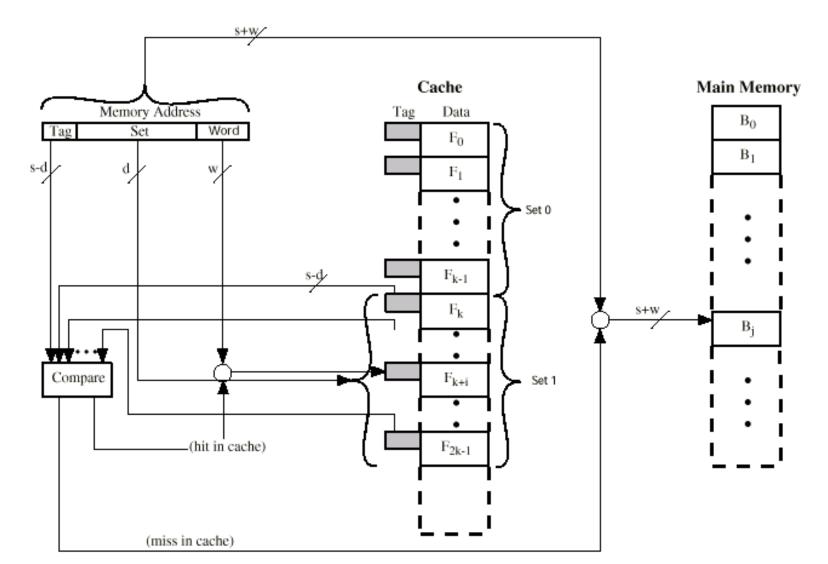

Processor-memory communication with a cache.

#### External communication.

To remedy this situation, many computers have a cache memory CM posstioned between the CPU and main memory. The cache CM is smaller and faster than main memory and may reside, wholly or in part, on the same chip as the CPU It typically permits the CPU to perform a memory load or store operation in a sizegle clock cycle, whereas a memory access that bypasses the cache and is handled by main memory takes many clock cycles. The cache is designed to be transparent to the CPU's instructions, which "see" the cache and main memory as forming a single, seamless memory space consisting of  $2^m$  addressable storage locations  $M(0), M(1), \dots, M(2^m-1)$ . In this chapter we will take this viewpoint and use M m refer to the external memory, whether or not a cache is present. A specific memory location in M with address adr is referred to as M(adr) or simply as adr. When necessary, we will use MM to distinguish the main memory from the cache memory CM, as in Figure 3.1b. The structure of caches and their interactions with main memory are further studied in Chapter 6.

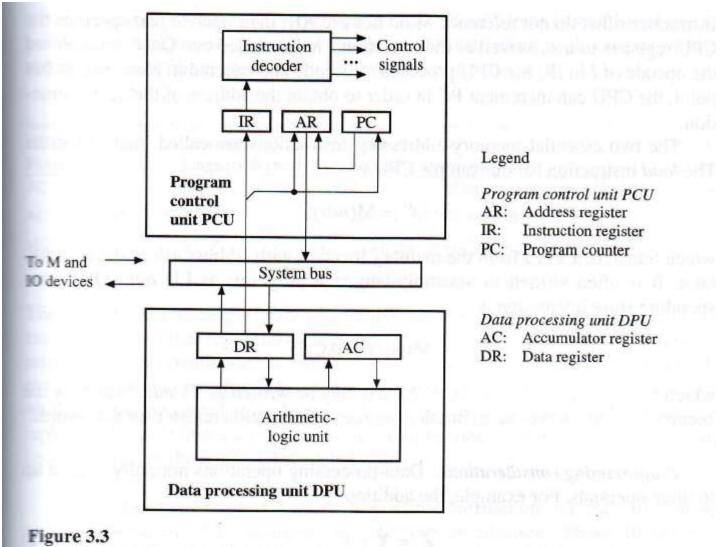

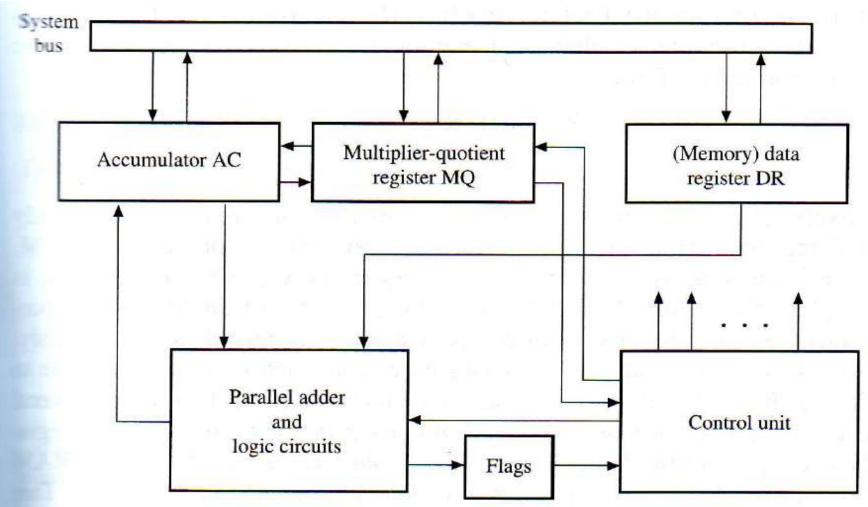

Accumulator-based CPU. Despite the improvements in IC technology over the years, CPU design continues to be based on the premise that the CPU should be as fast as the available technology and overall design requirements allow. Since cost generally increases with circuit complexity, the number of components in the CPU must be kept relatively small. The CPU organization proposed by von Neumann and his colleagues for the IAS computer (section 1.2.2) is the basis for most subsequent designs. It comprises a small set of registers and the circuits needed to execute a functionally complete set of instructions. In many early designs, one of the CPU registers, the accumulator,<sup>1</sup> played a central role, being used to store an input or output operand (result) in the execution of many instructions.

A small accumulator-based CPU.

Programming considerations. Data-processing operations normally require u to three operands. For example, the addition

(3)

$$Z := X + Y$$

has three distinct operands X, Y, and Z. The accumulator-based CPU of Figure 3 supports only *single-address* instructions, that is, instructions with one explicimemory address. However, AC and DR can serve as *implicit* operand locations s that multioperand operations can be implemented by executing several instruction in sequence. For example, a program to implement (3.2), assuming that X, Y, and all refer to data words in M, can take the following form:

|                |                              | 1000 CT 1000 CO 1000 CT 1000 C |

|----------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HDL<br>format  | Assembly-<br>language format | Narrative<br>format (comment)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AC := M(X);    | LD X                         | Load X from M into accumulator AC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DR := AC;      | MOV DR, AC                   | Move contents of AC to DR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| AC := M(Y);    | LD Y                         | Load Y into accumulator AC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AC := AC + DR; | ADD                          | Add DR to AC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| M(Z) := AC;    | ST Z                         | Store contents of AC in M.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Туре               | Instruction   | HDL<br>format                    | Assembly-<br>language format | Narrative<br>format (comment)                |

|--------------------|---------------|----------------------------------|------------------------------|----------------------------------------------|

| Data transfer      | Load          | AC := M(X)                       | LD X                         | Load X from M into AC.                       |

|                    | Store         | M(X) := AC                       | ST X                         | Store contents of AC in M as X.              |

|                    | Move register | DR := AC                         | MOV DR, AC                   | Copy contents of AC to DR                    |

|                    | Move register | AC := DR                         | MOV AC, DR                   | Copy contents of DR to AC                    |

| Data               | Add           | AC := AC + DR                    | ADD                          | Add DR to AC.                                |

| processing         | Subtract      | AC := AC - DR                    | SUB                          | Subtract DR from AC.                         |

|                    | And           | AC := AC and DR                  | AND                          | And bitwise DR to AC.                        |

|                    | Not           | AC := not AC                     | NOT                          | Complement contents of AC                    |

| Program<br>control | Branch        | PC := M(adr)                     | BRA adr                      | Jump to instruction with<br>address adr.     |

|                    | Branch zero   | if $AC = 0$ then<br>PC := M(adr) | BZ adr                       | Jump to instruction <i>adr</i> if<br>AC = 0. |

## Figure 3.4

Instruction set for the CPU of Figure 3.3.

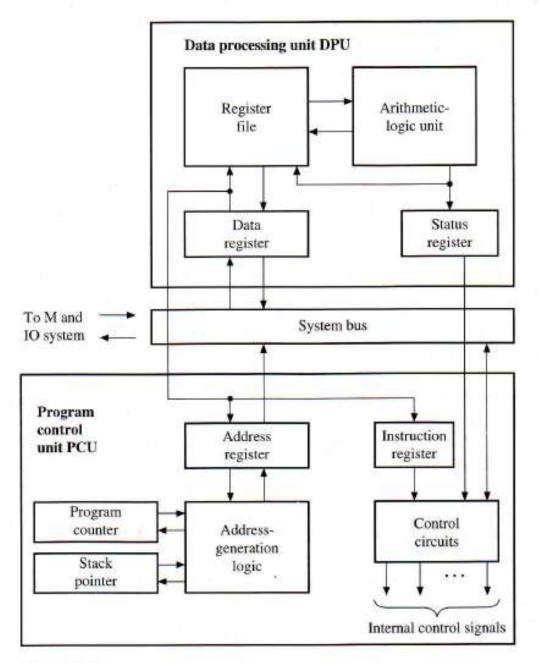

## **31.2** Additional Features

Next we examine some more advanced features of CPUs and look at representative commercial microprocessors of the RISC and CISC types.

Architecture extensions. There are many ways in which the basic design of Figure 3.3 can be improved. Most recent CPUs contain the following extensions, which significantly improve their performance and ease of programming.

- Multipurpose register set for storing data and addresses: These replace the accumulator AC and the auxiliary registers DR and AR of our basic CPU. The resulting CPU is sometimes said to have the *general register organization* exemplified by the thirdgeneration IBM System/360-370 (Figure 1.17), which has 32 such registers. The set of general registers is now usually referred to as a *register file*.

- Additional data, instruction, and address types: Most CPUs have instructions to handle data and addresses with several different word sizes and formats. Although some microprocessors have only add and subtract instructions in the arithmetic category, relatively little extra circuitry is required for (fixed-point) multiply and divide instructions, which simplify many programming tasks. Call and return instructions also simplify program design.

- Register to indicate computation status: A status register (also called a condition code or flag register) indicates infrequent or exceptional conditions resulting from the instruction execution. Examples are the appearance of an all-zero result or an invalid instruction like divide by zero. A status register can also indicate the user and supervisor states. Conditional branch instructions can test the status register, which simplifies the programming of conditional actions.

#### Figure 3.7

A typical CPU with the general register organization.

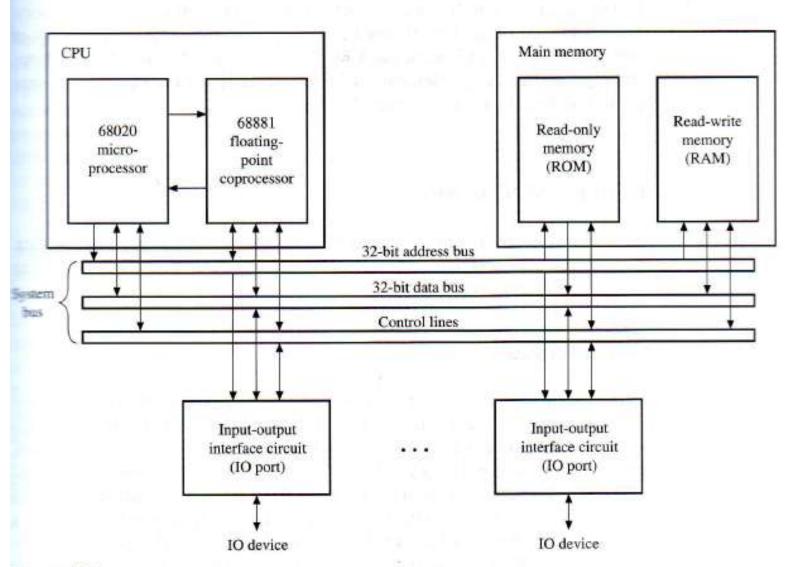

**Coprocessors.** The built-in instruction repertoire of the 68020 includes fixedmultiplication and division and stack-based instructions for transferring conmiletween programs. Hardware-implemented floating-point instructions are not miletween programs. Hardware-implemented floating-point instructions for a auxiliary the 68881 floating-point coprocessor. (The ARM6 also has provisions for memal coprocessors.) In general, a *coprocessor P* is a specialized instruction exemed by P can be included to a microprocessor so that instructions to be exemed by P can be included in programs fetched by the microprocessor. Thus the processor serves as an extension to the microprocessor and forms part of the TU as indicated in Figure 3.14.

68020-based microcomputer with floating-point coprocessor.

### INSTRUCTION SETS

Next we turn to the representation, selection, and application of instruction set. This topic embraces opcode and operand formats, the design of the instruction types to include in a processor's instruction set, and the use of instructions in each cutable programs.

#### 3.3.1 Instruction Formats

The purpose of an instruction is to specify both an operation to be carried out by CPU or other processor and the set of operands or data to be used in the operation. The operands include the input data or arguments of the operation and the result that are produced.

Introduction. Most instructions specify a register-transfer operation of the form

$$X_1 := op(X_1, X_2, ..., X_n)$$

which applies the operation op to n operands  $X_1, X_2, ..., X_n$ , where n ranges from zero to four or so. We can write the same instruction in the assembly-language notation

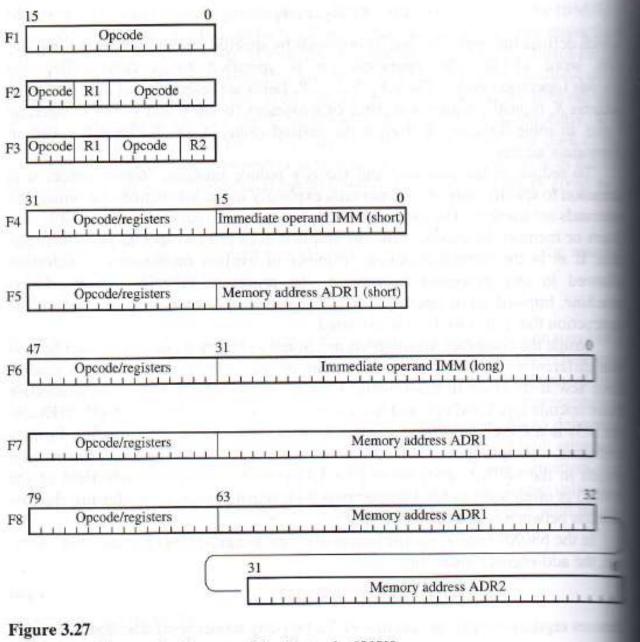

A selection of instruction formats of the Motorola 680X0.

Instructions are conveniently divided into the following five types:

- Data-transfer instructions, which copy information from one location to another either in the processor's internal register set or in the external main memory.

- 2. Arithmetic instructions, which perform operations on numerical data.

- 3. Logical instructions, which include Boolean and other nonnumerical operations

- Program-control instructions, such as branch instructions, which change the sequence in which programs are executed.

- Input-output (IO) instructions, which cause information to be transferred between the processor or its main memory and external IO devices.

| Туре      | Operation name(s) | Description                                                    |  |

|-----------|-------------------|----------------------------------------------------------------|--|

| Testa     | MOVE              | Copy word or block from source to destination.                 |  |

| minsfer   | LOAD              | Copy word from memory to processor register.                   |  |

|           | STORE             | Copy word from processor register to memory.                   |  |

|           | SWAP (EXCHANGE)   | Swap contents of source and destination.                       |  |

|           | CLEAR             | Transfer word of 0s to destination.                            |  |

|           | SET               | Transfer word of 1s to destination.                            |  |

|           | PUSH              | Transfer word from source to top of stack.                     |  |

|           | POP               | Transfer word from top of stack to destination.                |  |

| Amthmetic | ADD               | Compute sum of two operands.                                   |  |

|           | ADD WITH CARRY    | Compute sum of two operands and a carry bit.                   |  |

|           | SUBTRACT          | Compute difference of two operands.                            |  |

|           | MULTIPLY          | Compute product of two operands.                               |  |

|           | DIVIDE            | Compute quotient (and remainder) of two operands.              |  |

|           | MULITPLY AND ADD  | Compute product of two operands; add it to a third<br>operand. |  |

|           | ABSOLUTE          | Replace operand by its absolute value.                         |  |

|           | NEGATE            | Change sign of operand.                                        |  |

|           | INCREMENT         | Add 1 to operand.                                              |  |

|           | DECREMENT         | Subtract 1 from operand.                                       |  |

|           | ARITHMETIC SHIFT  | Shift operand left (right) with sign extension.                |  |

| Logical   | AND )             |                                                                |  |

|           | OR                | Perform the specified logical operation bitwise.               |  |

|           | NOT               |                                                                |  |

|           | EXCLUSIVE-OR      |                                                                |  |

|           | LOGICAL SHIFT     | Shift operand left (right) introducing 0s at end.              |  |

|           | ROTATE            | Left- (right-) shift operand around closed path.               |  |

|           | CONVERT (EDIT)    | Change data format, for example, from binary to decima         |  |

| Program | JUMP (BRANCH)                | Unconditional transfer; load PC with specified address.                                                          |

|---------|------------------------------|------------------------------------------------------------------------------------------------------------------|

| control | JUMP CONDITIONAL             | Test specified conditions; if true, load PC with specified<br>address.                                           |

|         | JUMP TO SUBROUTINE           | Place current program control information including PC in                                                        |

|         | (BRANCH-AND-LINK)            | known location, for example, top of stack; jump to<br>specified address.                                         |

|         | RETURN                       | Restore current program control information including PC<br>from known location, for example, from top of stack. |

|         | EXECUTE                      | Fetch operand from specified location and execute as<br>instruction; note that PC is not modified.               |

|         | SKIP CONDITIONAL             | Test specified condition; if true, increment PC to skip next instruction.                                        |

|         | TRAP (SOFTWARE<br>INTERRUPT) | Enter supervisor mode.                                                                                           |

|         | TEST                         | Test specified condition; set flag(s) based on outcome.                                                          |

|         | COMPARE                      | Make logical or arithmetic comparison of two or more<br>operands; set flag(s) based on outcome.                  |

Figure 3.34 List of common instruction types.

| Туре               | Operation name(s)        | Description                                                                                                                      |

|--------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Program<br>control | SET CONTROL<br>VARIABLES | Large class of instructions to set controls for protection pur-<br>poses, interrupt handling, timer control, and so forth (often |

| contor             | The black                | privileged).                                                                                                                     |

|                    | WAIT (HOLD)              | Stop program execution; test a specified condition continu-<br>ously; when the condition is satisified, resume instruction       |

|                    |                          | execution.                                                                                                                       |

|                    | NO OPERATION             | No operation is performed, but program execution continues.                                                                      |

| Input-output       | INPUT (READ)             | Copy data from specified IO port to destination, for example,<br>output contents of a memory location or processor register      |

|                    | OUTPUT (WRITE)           | Copy data from specified source to IO port.                                                                                      |

|                    | START IO                 | Transfer instuctions to IOP to initiate an IO operation.                                                                         |

|                    | TEST IO                  | Transfer status information from IO system to specified dem<br>nation.                                                           |

|                    | HALT IO                  | Transfer instructions to IOP to terminate an IO operation.                                                                       |

# Unit - 02 Principles of Computer design

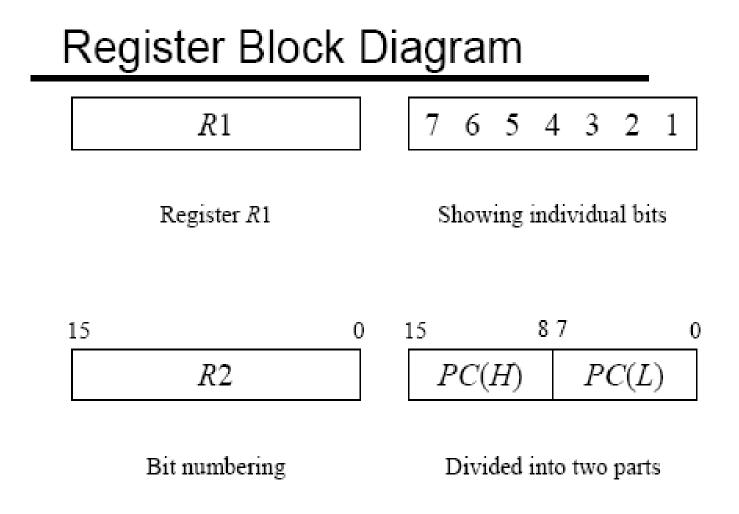

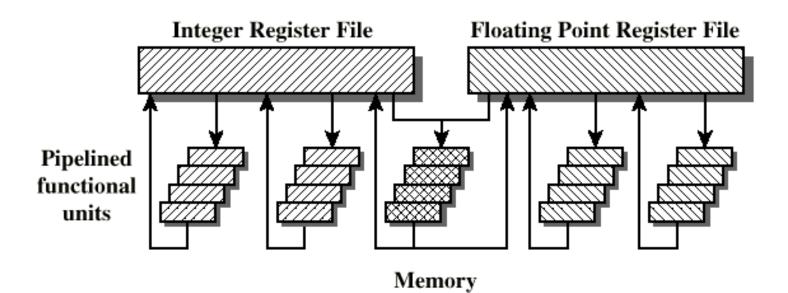

# Register Organization Digital System Overview

- Each module is built from digital components

- Registers

- Decoders

- Arithmetic elements

- Control logic

- Modules connected by common data and control paths

- Collection of modules is a digital system

# Internal Hardware Organization

- Can be defined by specifying

- Set of registers and their functions

- Sequence of microoperations performed on register data

- Control that initiates the sequence of microoperations

- Can use words to express sequence of microoperations, but it's better to use a notation and symbols

- Register Transfer Language

# Registers

- Capital letter sometimes followed by a number

- MAR memory address register

- PC program counter

- IR instruction register

- R1, R2 processor register 1, process register 2

- Each flip-flop in a *n*-bit register is numbered from *n*-1 to 0 from left to right

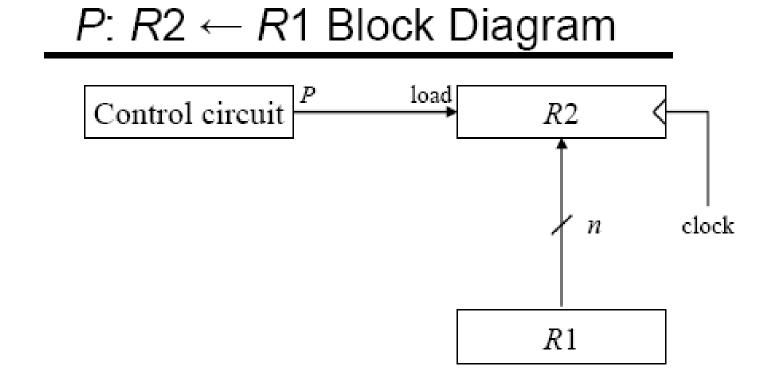

# **Register Transfer**

- Use replacement operator:  $\leftarrow$

- $R2 \leftarrow R1$

- Transfer contents of *R*1 to *R*2 at next clock pulse

- Contents of R1 unchanged

- Circuits are available from outputs of source register to inputs of destination register

- Destination register has parallel load capability

# **Control Function**

- Control condition

- Boolean variable (equal to 0/false or 1/true)

- Terminated with colon

- Prefix to register transfer statement

- $P: R2 \leftarrow R1$

- $\blacksquare$  Transfer happens at next clock pulse while P =1

# 2<sup>nd</sup> Register Transfer Example

- $T: R2 \leftarrow R1, R1 \leftarrow R2$

- Comma used to separate multiple register transfers that happen at the same time

- This register swap is possible using edgetriggered flip-flops

# **Using Parentheses**

- R1(8–15) or R1(H)

- if R1 is 16-bit register

- Indicates high-order byte, leftmost 8 bits

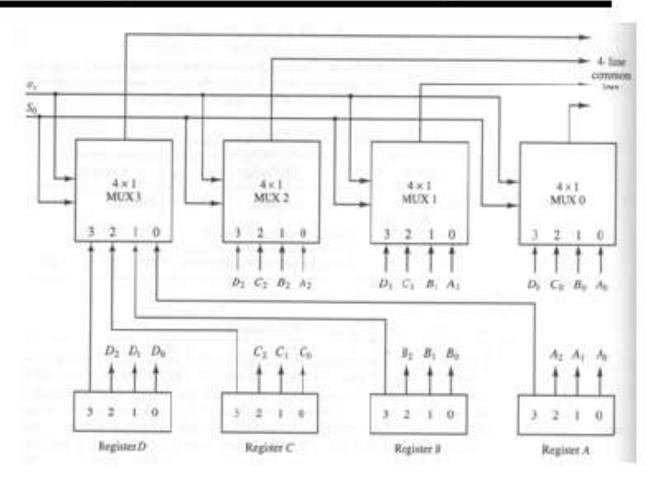

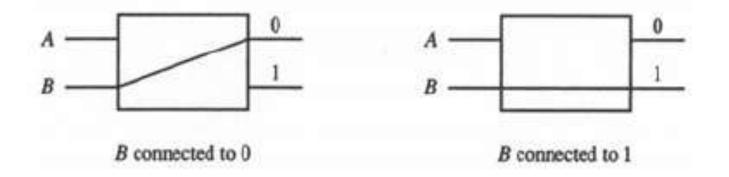

# **Bus Transfers**

- Wiring each register to every other register requires an excessive number of data lines

- Use common bus system instead

- One data line for each register bit

- Control signal lines used for register selection

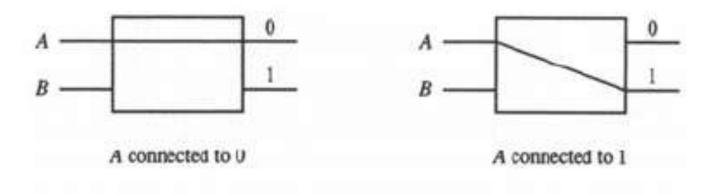

- Use multiplexers to select source register to put data on common bus

- Activate load control of destination register to load data from common bus

# **Bus System For 4 Registers**

#### **Bus Details**

- Multiplex k registers with n bits each to build n-line common bus

- Need n multiplexers

- Each multiplexer has k input lines

- One for each register

- $BUS \leftarrow C, R1 \leftarrow BUS$  can be rewritten as  $R1 \leftarrow C$

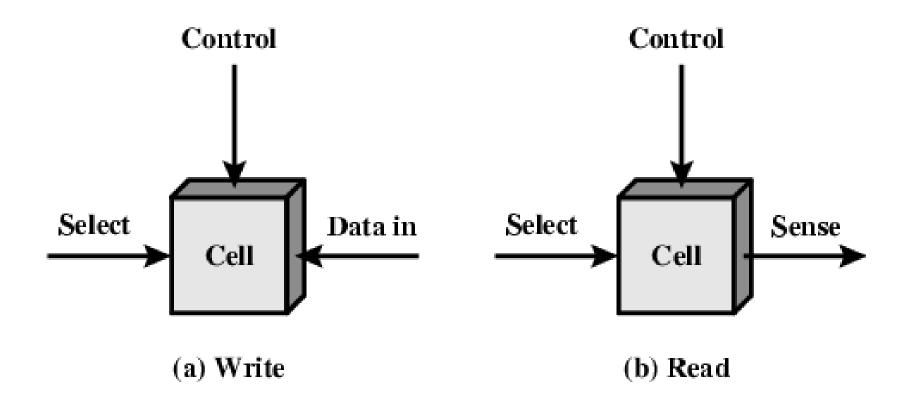

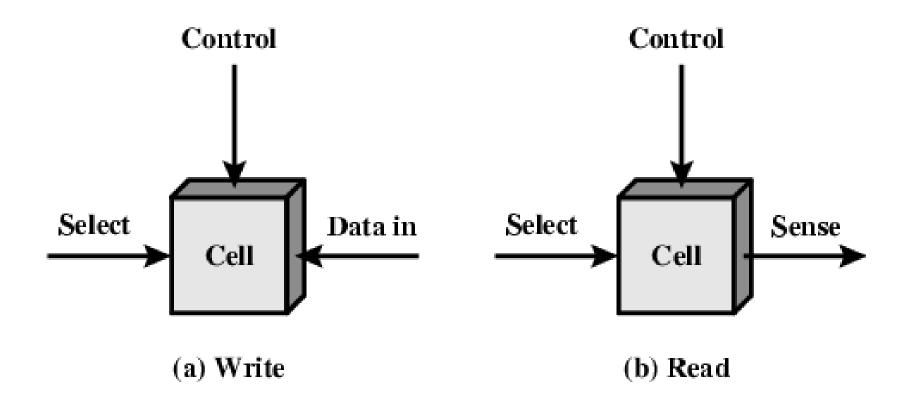

# Memory Transfer

- Read: from memory to outside world

- Write: from outside world into memory

- Memory word is called M

- Address Register is called AR

- Data Register is called DR

- Read:  $DR \leftarrow M[AR]$

- Write:  $M[AR] \leftarrow DR$

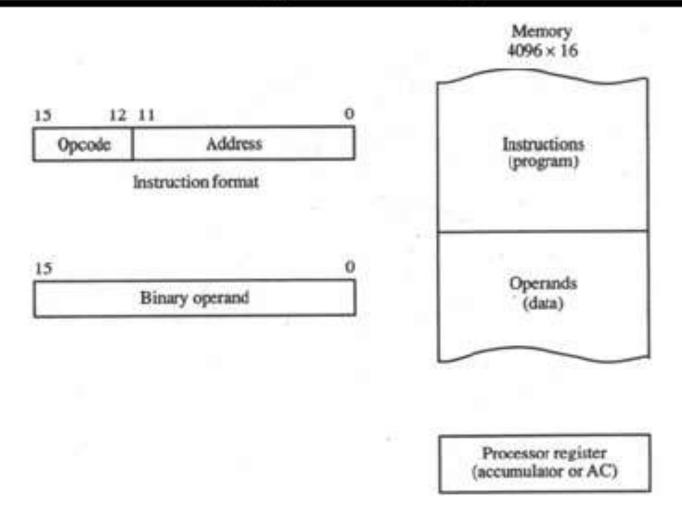

#### Instruction Code

- Computer instruction is binary code that specifies a sequence of microoperations

- Operation code + Address

- Op code must have n bits for ≤ 2<sup>n</sup> operations

- Op code sometimes called a macrooperation

- Address is register or memory location

- Memory location is operand address

- Shorten "instruction code" to "instruction"

- · Instructions and data in memory

# Stored Program Organization

- One processor register

- $\blacksquare AC accumulator$

- Instruction format

- 4-bit op code

- 12-bit address (for 2<sup>12</sup> = 4096 memory words)

- Instruction execution cycle

- Read 16-bit instruction from memory

- Use 12-bit address to fetch operand from memory

- Execute 4-bit op code

## Stored Program Organization

# Address Types

- 12-bit instruction address

- Immediate

- Actual data value

- Direct

- Memory address where data (operand) resides

- Indirect

- Memory address where memory address of data (operand) resides

- Effective address is the address of the operand

- Lead bit of instruction used as indirect flag

#### Direct / Indirect Address

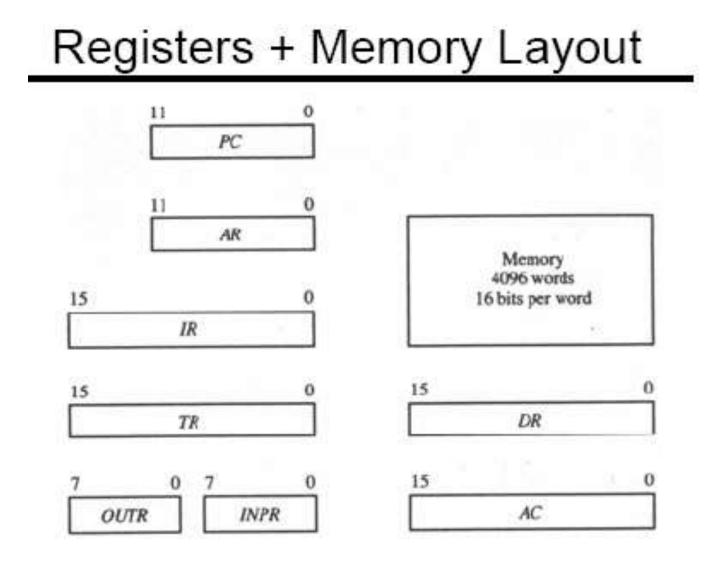

### **Basic Computer Registers**

| Register<br>symbol | Number<br>of bits | Register name        | Function                     |

|--------------------|-------------------|----------------------|------------------------------|

| DR                 | 16                | Data register        | Holds memory operand         |

| AR                 | 12                | Address register     | Holds address for memory     |

| AC                 | 16                | Accumulator          | Processor register           |

| IR                 | 16                | Instruction register | Holds instruction code       |

| PC                 | 12                | Program counter      | Holds address of instruction |

| TR                 | 16                | Temporary register   | Holds temporary data         |

| INPR               | 8                 | Input register       | Holds input character        |

| OUTR               | 8                 | Output register      | Holds output character       |

## Program Counter (PC)

- Holds memory address of next instruction

- Next instruction is fetched after current instruction completes execution cycle

- *PC* is incremented right after instruction is fetched from memory

- PC value can be replaced by new address when executing a branch instruction

### **Register Control Inputs**

- Load (LD)

- Increment (INR)

- Clear (CLR)

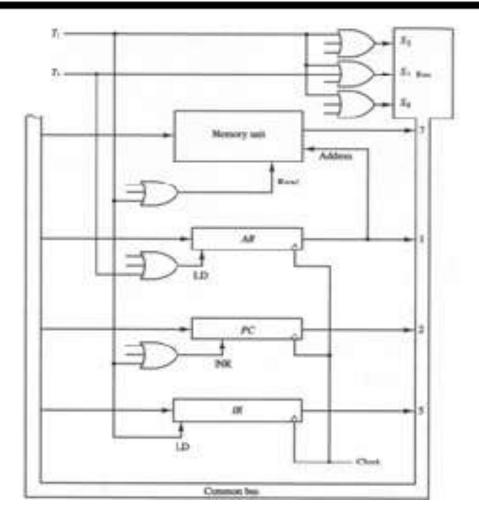

### Common Bus

- Connects registers and memory

- Specific output selected by S<sub>2</sub>S<sub>1</sub>S<sub>0</sub>

- When register has < 16 bits, high-order bus bits are set to 0

- Register with LD enabled reads data from bus

- · Memory with Write enabled reads bus

- Memory with Read enabled puts data on bus

When S<sub>2</sub>S<sub>1</sub>S<sub>0</sub> = 111

## Address Register (AR)

- Always used to specify address within memory unit

- Dedicated register eliminates need for separate address bus

- Content of any register output connected to the bus can be written to memory

- Any register input connected to bus can be target of memory read

- As long as its LD is enabled

## Accumulator (AC)

- Input comes from adder and logic circuit

- Adder and logic circuit

- Input

- ♦ 16-bit output of AC

- 16-bit data register (DR)

- 8-bit input register (INPR)

- Output

- ♦ 16-bit input of AC

- E flip-flop (extended AC bit, aka overflow)

- *DR* and *AC* input used for arithmetic and logic microoperations

# Timing Is Everything

- Content of any register output connected to the bus can be applied to the bus and content of any register input connected to the bus can be loaded from the bus during the same clock cycle

- These 2 microoperations can be executed at the same time

$DR \leftarrow AC$  and  $AC \leftarrow DR$

## **Bus Connections**

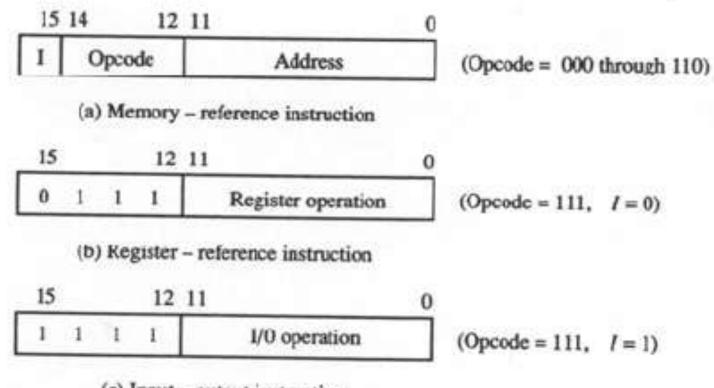

# Basic Instruction Formats

(c) Input - output instruction

# Instruction Format

- Only 3 bits used for op code

- Looks like only 8 different op codes are possible

- Wrong!

- For op code 111, one of the low-order 12 bits is turned on to extend the op code definition

# **Basic Instructions**

|        | Hexadecimal code |       |                                      |

|--------|------------------|-------|--------------------------------------|

| Symbol | l = 0            | I = 1 | Description                          |

| AND    | 0xxx             | 8113  | AND memory word to AC                |

| ADD    | 1XXX             | 9888  | Add memory word to AC                |

| LDA    | 2000             | Axx   | Load memory word to AC               |

| STA    | JANK             | Baxa  | Store content of AC in memory        |

| BUN    | 4xxx             | Cxxx  | Branch unconditionally               |

| BSA    | SAXE.            | Dam   | Branch and save return address       |

| ISZ    | fixes            | Exx   | Increment and skip if zero           |

| CLA    | 7100             |       | Clear AC                             |

| CLE    | 7                | 00    | Clear E                              |

| CMA    | 7.               | 100   | Complement AC                        |

| CME    | 7100             |       | Complement E                         |

| CID    |                  | 090   | Circolate right 4C and F             |

| CIL    | 7                | 940   | Circulate left AC and E              |

| INC    | 7020             |       | Increment AC                         |

| SPA    | 7010             |       | Skip next instruction if AC positive |

| SNA    | 7908             |       | Skip next instruction if AC negative |

| SZA    | 7904             |       | Skip next instruction if AC zero     |

| 375    | 7904             |       | Skip near innersedous il II is 0     |

| HLT    | 7901             |       | Halt computer                        |

| INF    | F800             |       | Input character to AC                |

| OUT    | E400             |       | Output character from AC             |

| SK1    | F200             |       | Stip on input flag                   |

| SKD    | F100             |       | Skip on output flag                  |

| ION    | F                | 080   | Interrupt on                         |

| IOF    | F                | 040   | Interrupt off                        |

# Instruction Set Completeness

- Arithmetic, logical, and shift

- Move data from and to memory and registers

- Program control and status check

- Input and output

- (I/O, I/O, it's off to the bus we go...)

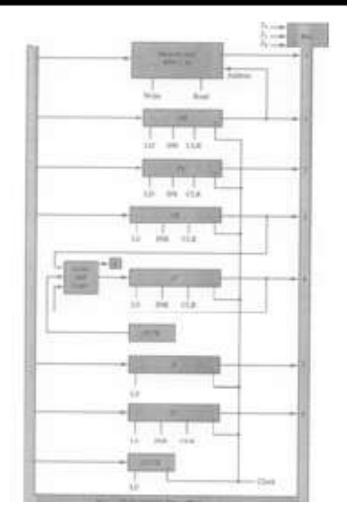

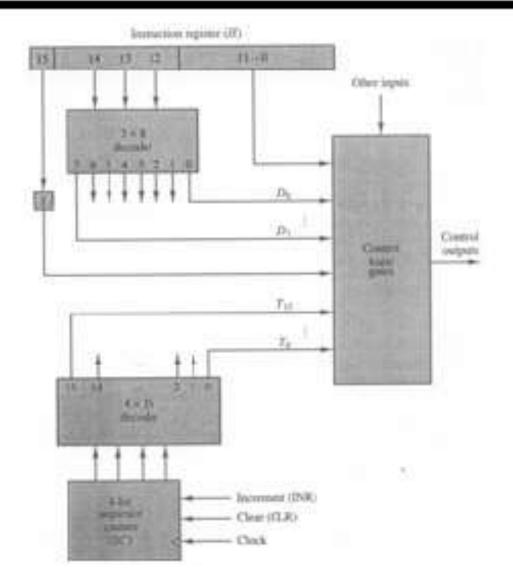

# Control Unit

- Instruction read from memory and put in  $I\!R$

- Leftmost bit put in I flip-flop

- 3-bit op code decoded with 3 x 8 decoder into D<sub>0</sub> to D<sub>7</sub>

- 4-bit sequence counter (SC) decoded with 4 x 16 decoder into T<sub>0</sub> to T<sub>15</sub> (timing signals)

- I, D<sub>0</sub> to D<sub>7</sub>, T<sub>0</sub> to T<sub>15</sub>, rightmost 12 bits of IR, and other inputs are fed into control and logic gates

# Control Unit

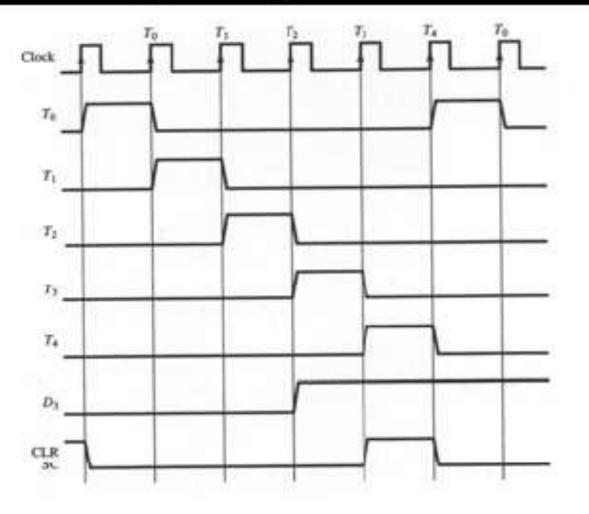

# Sequence Counter (SC)

- Inputs are increment (INR) and clear (CLR)

- Example

- SC incremented to provide  $T_0$ ,  $T_1$ ,  $T_2$ ,  $T_3$ , and  $T_4$

- At time  $T_4$ , SC is cleared to 0 if  $D_3$  is active

- Written as:  $D_3T_4$ :  $SC \leftarrow 0$

# **Timing Diagram**

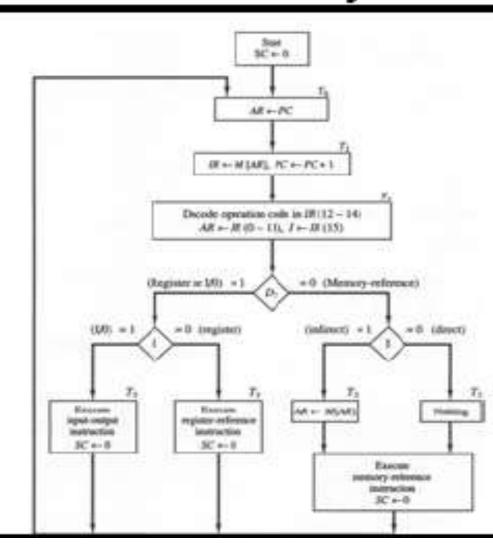

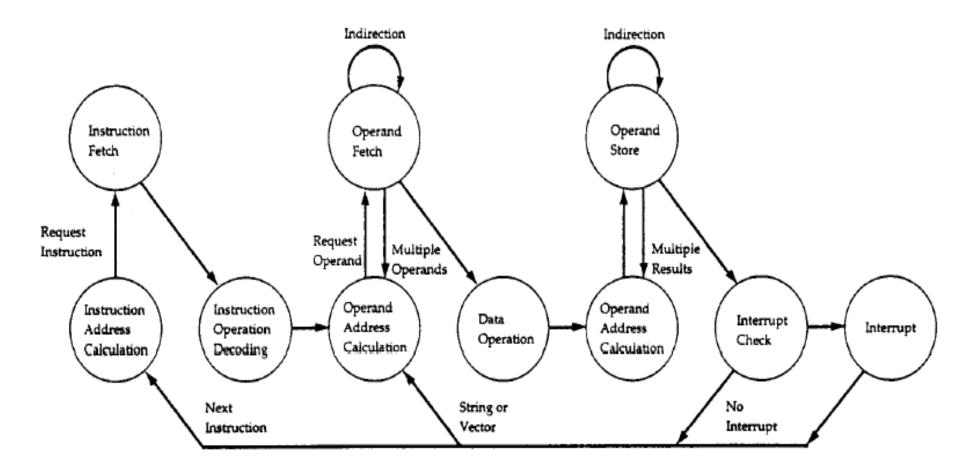

# Instruction Cycle

- Fetch instruction from memory

- Decode the instruction

- Read effective address from memory if indirect address

- Execute the instruction

## Fetch And Decode

- SC cleared to 0, generating timing signal T<sub>0</sub>

- After each clock pulse, SC is incremented

- Fetch and decode microoperations

$$\blacksquare T_0: AR \leftarrow PC$$

$$\blacksquare T_1: IR \leftarrow M[AR], \\ PC \leftarrow PC + 1$$

■  $T_2: D_0, \dots D_7 \leftarrow \text{decode } IR(12\text{-}14),$   $AR \leftarrow IR(0\text{-}11),$  $I \leftarrow IR(15)$

## Fetch Phase

# Determining The Type of Instruction Instruction Cycle Flowchart

# Instruction Paths

- $D'_7 IT_3$ :  $AR \leftarrow M[AR]$

- $D'_7 I' T_3$ : Do nothing

- $D_7 I' T_3$ : Execute a register-reference instruction

- D<sub>7</sub>IT<sub>3</sub>: Execute an I/O instruction

#### **Register-Reference Instructions**

$D_7 I' I_3 = r$  (common to all register-reference instructions)  $IR(i) = B_i$  [bit in IR(0-11) that specifies the operation]

|     | F:         | SC -0                                                                   | Clear |

|-----|------------|-------------------------------------------------------------------------|-------|

| CLA | rB11:      | $AC \leftarrow 0$                                                       | Clear |

| CLE | rB10:      | $E \leftarrow 0$                                                        | Clear |

| CMA | rBy:       | $AC \leftarrow \overline{AC}$                                           | Com   |

| CME | $rB_{s}$ : | $E \leftarrow E$                                                        | Com   |

| CIR | rB1:       | $AC \leftarrow \text{shr } AC, AC(15) \leftarrow E, E \leftarrow AC(0)$ | Circu |

| CIL | rB6:       | $AC \leftarrow shl AC, AC(0) \leftarrow E, E \leftarrow AC(15)$         | Circu |

| INC | rBs:       | $AC \leftarrow AC + 1$                                                  | Incic |

| SPA | rB4:       | If $(AC(15) = 0)$ then $(PC \leftarrow PC + 1)$                         | Skip  |

| SNA | rB3:       | If $(AC(15) = 1)$ then $(PC \leftarrow PC + 1)$                         | Skip  |

| SZA | rR2.       | If $(AC = 0)$ then $PC \leftarrow PC + 1$                               | Skip  |

| SZE | $rB_1$ :   | If $(E = 0)$ then $(PC \leftarrow PC + 1)$                              | Skip  |

| HLT | $rB_0$ :   | $S \leftarrow 0$ (S is a start-stop flip-flop)                          | Halt  |

Clear SC Clear AC Clear E Complement AC Complement E Circulate right Circulate left Increment AC Skip if positive Skip if negative Skip if AC zero Skip if E zero Halt computer

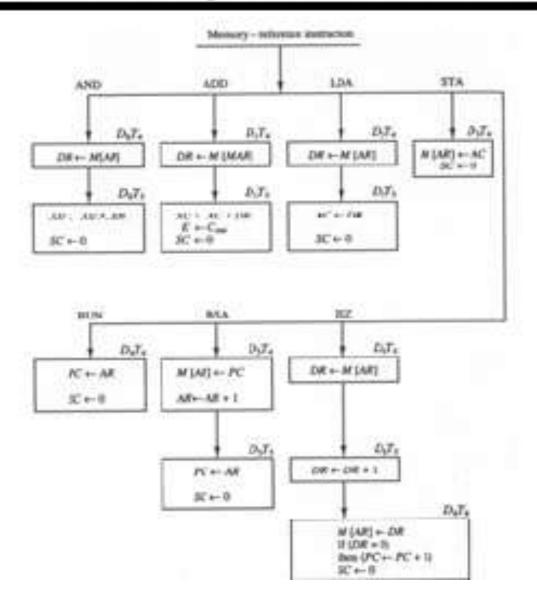

## Memory-Reference Instructions

| Symbol | Operation decoder | Symbolic description                             |

|--------|-------------------|--------------------------------------------------|

| AND    | $D_0$             | $AC \leftarrow AC \land M[AR]$                   |

| ADD    | $D_1$             | $AC \leftarrow AC + M[AR], E \leftarrow C_{out}$ |

| LDA    | $D_2$             | $AC \leftarrow M[AR]$                            |

| STA    | $D_3$             | $M[AR] \leftarrow AC$                            |

| BUN    | $D_4$             | $PC \leftarrow AR$                               |

| BSA    | $D_5$             | $M[AR] \leftarrow PC, PC \leftarrow AR + 1$      |

| ISZ    | $D_6$             | $M[AR] \leftarrow M[AR] + 1,$                    |

|        |                   | If $M[AR] + 1 = 0$ then $PC \leftarrow PC +$     |

#### AND to AC

- $D_0T_4: DR \leftarrow M[AR]$

- $D_0T_5: AC \leftarrow AC \wedge DR, SC \leftarrow 0$

## ADD to AC

- $D_1T_4: DR \leftarrow M[AR]$

- $D_1T_5: AC \leftarrow AC + DR, E \leftarrow C_{out}, SC \leftarrow 0$

#### LDA: Load AC

- $D_2T_4: DR \leftarrow M[AR]$

- $D_2T_5: AC \leftarrow DR, SC \leftarrow 0$

### STA: Store AC

•  $D_3T_4: M[AR] \leftarrow AC, SC \leftarrow 0$

### **BUN: Branch Unconditionally**

•  $D_4T_4: PC \leftarrow AR, SC \leftarrow 0$

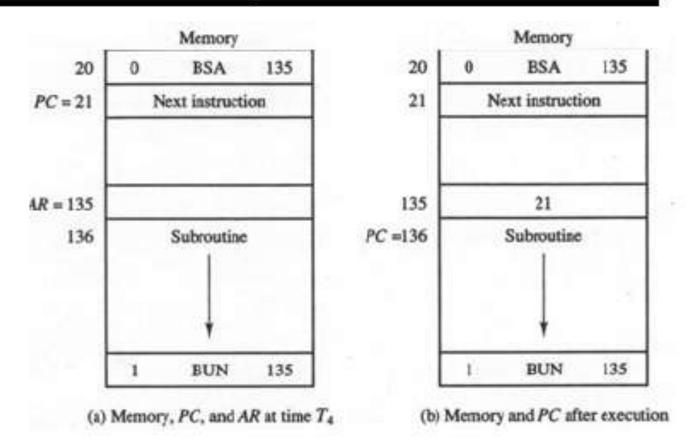

### BSA: Branch & Save Return Address

- $D_5T_4: M[AR] \leftarrow PC, AR \leftarrow AR + 1$

- $D_5T_5$ :  $PC \leftarrow AR$ ,  $SC \leftarrow 0$

#### BSA Example

## ISZ: Increment & Skip if Zero

- Increment word specified by effective address

If value = 0, increment PC

- $D_6T_4: DR \leftarrow M[AR]$

- $D_6T_5$ :  $DR \leftarrow DR + 1$

- $D_6T_6: M[AR] \leftarrow DR, SC \leftarrow 0,$ if (DR = 0) then  $(PC \leftarrow PC + 1)$

# Memory-Reference Instructions

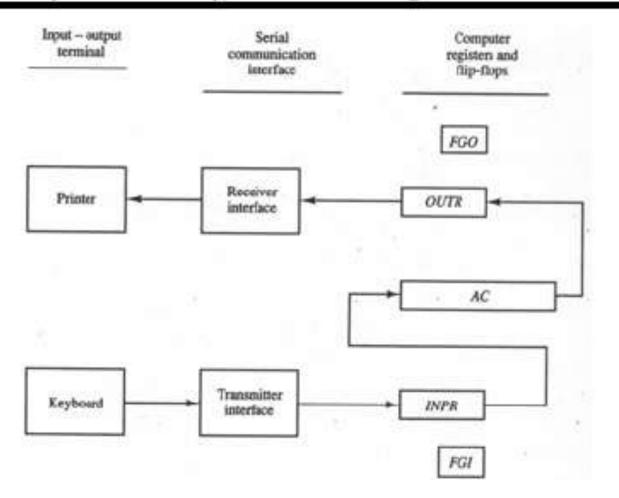

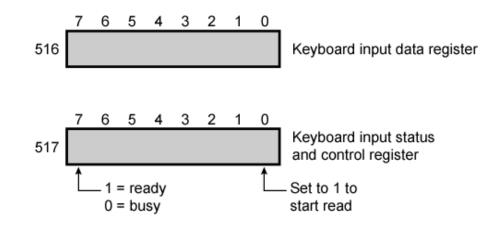

## Input Register INPR

- 1-bit input flip-flop *FGI*

- Initially cleared to 0

- When key hit on keyboard

- 8-bit alphanumeric code is shifted into INPR

- Input flag FGI set to 1

- No more input can be accepted from keyboard

- Computer checks FGI, when set to 1

- Parallel transfer from *INPR* to *AC*

- FGI cleared to 0

- More input can now be accepted from keyboard

## Output Register OUTR

- 1-bit output flip-flop FGO

Initially set to 1

- Computer checks FGO, when set to 1

- Parallel transfer from AC to OUTR

- FGO cleared to 0

- No more output can be sent from computer

- Output device accepts 8-bit character

- FGO set to 1

- More output can now be sent from computer

#### Input-Output Configuration

## Input-Output Instructions

$D_7 I T_3 = p$  (common to all input-output instructions)  $IR(i) = B_i$  [bit in IR(6-11) that specifies the instruction]

|     | <i>p</i> :               | $SC \leftarrow 0$                            | C |

|-----|--------------------------|----------------------------------------------|---|

| INP | pB11:                    | $AC(0-7) \leftarrow INPR, FGI \leftarrow 0$  | I |

| OUT | pB10:                    | $OUTR \leftarrow AC(0-7), FGO \leftarrow 0$  | C |

| SKI | pB9:                     | If $(FGI = 1)$ then $(PC \leftarrow PC + 1)$ | S |

| SKO | $pB_8$ :                 | If $(FGO = 1)$ then $(PC \leftarrow PC + 1)$ | S |

| ION | pB7:                     | IEN ←1                                       | I |

| IOF | <i>pB</i> <sub>6</sub> : | $IEN \leftarrow 0$                           | I |

Clear SC Input character Output character Skip on input flag Skip on output flag Interrupt enable on Interrupt enable off

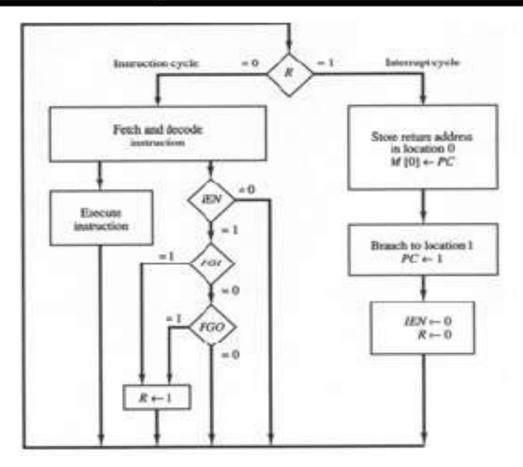

## Interrupt Enable IEN

- Having computer constantly check FGI and FGO via an executable instruction is a waste of time

- Instead, *IEN* is programmatically set, effectively saying "let me know if you need me"

- Meanwhile, it keeps executing instructions

- During each execution cycle, if computer detects *FGI* or *FGO* is set, then *R* is set to 1

- The interrupt happens when the computer is ready to fetch the next instruction

- R = 0 means go through instruction cycle

- R = 1 means go through interrupt cycle

#### Interrupt Flowchart

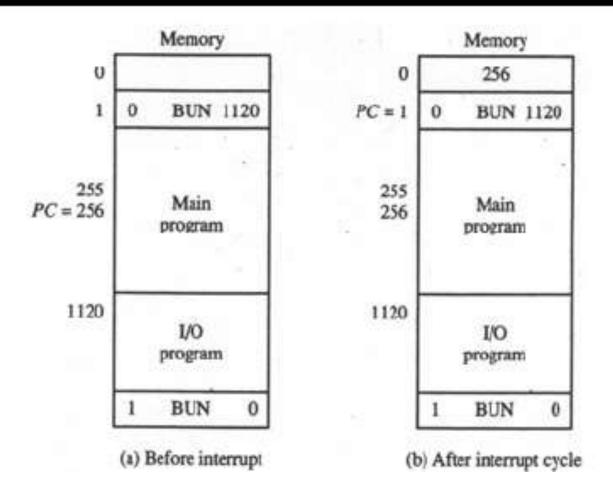

### Interrupt Cycle Example

## Interrupt Cycle

- Condition for setting *R* to 1  $T'_0T'_1T'_2(IEN)(FGI + FGO): R \leftarrow 1$

- Fetch phase modified to service interrupt RT<sub>0</sub>: AR ← 0, TR ← PC RT<sub>1</sub>: M[AR] ← TR, PC ← 0 RT<sub>2</sub>: PC ← PC + 1, IEN ← 0, R ← 0, SC ← 0

### Microoperation

- Elementary operation performed on data within one or more registers

- Operation result could update same register or another register

- Examples: shift, count, clear, and load

- Counter with parallel load can perform count and load

- Bidirectional shift can shift left or shift right

## **Microoperation Summary**

- Transfer data from one register to another (already covered)

- Perform arithmetic operations on numeric data stored in registers

- Manipulate bits on non-numeric data in registers

- Shift bits on data stored in registers

### Arithmetic Microoperations

- Addition

- Subtraction

- Increment

- Decrement

- Shift

#### Add and Subtract

- Add:  $R3 \leftarrow R1 + R2$

- Subtract:  $R3 \leftarrow R1 \underline{R2}$  $R3 \leftarrow R1 + \underline{R2} + 1$

Add 2's complement of R2

### Arithmetic Microoperations

| Symbols                                | Description                    |

|----------------------------------------|--------------------------------|

| $R3 \leftarrow R1 + R2$                | Contents R1 plus R2 put in R3  |

| $R3 \leftarrow R1 - R2$                | Contents R1 minus R2 put in R3 |

| $R2 \leftarrow \overline{R2}$          | 1's complement what's in R2    |

| $R2 \leftarrow \overline{R2} + 1$      | 2's complement what's in R2    |

| $R3 \leftarrow R1 + \overline{R2} + 1$ | R1 plus 2's complement of R2   |

| $R1 \leftarrow R1 + 1$                 | Increment R1 by 1              |

| $R1 \leftarrow R1 - 1$                 | Decrement R1 by 1              |

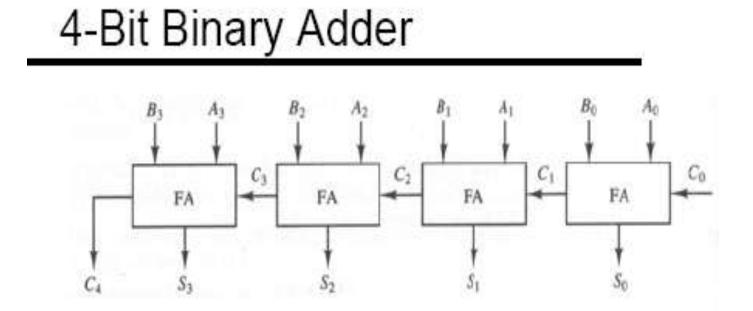

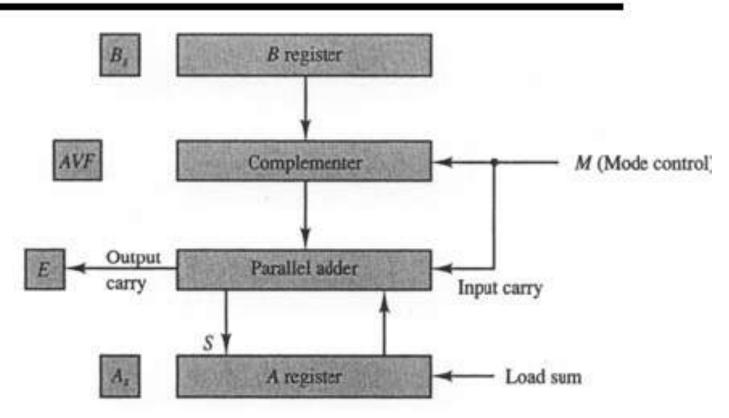

### **Binary Adder**

- Full-adder is a digital circuit that generates the arithmetic sum of two bits and a previous carry

- Binary-adder is a digital circuit that generates the arithmetic sum of two binary numbers of any length

- Constructed with full-adder circuits

- $\blacklozenge$  Output carry of one FA connected to input carry of next

- $\blacksquare$  *n*-bit binary adder requires *n* full-adders

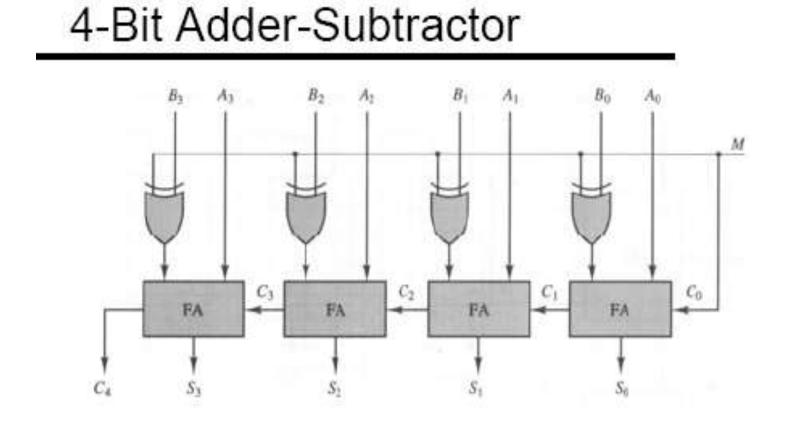

### **Binary Adder-Subtractor**

- Addition and subtraction combined into one common circuit by including an XOR gate with each FA

- Mode input M controls the operation

- Adder: M = 0

- Subtractor: M = 1

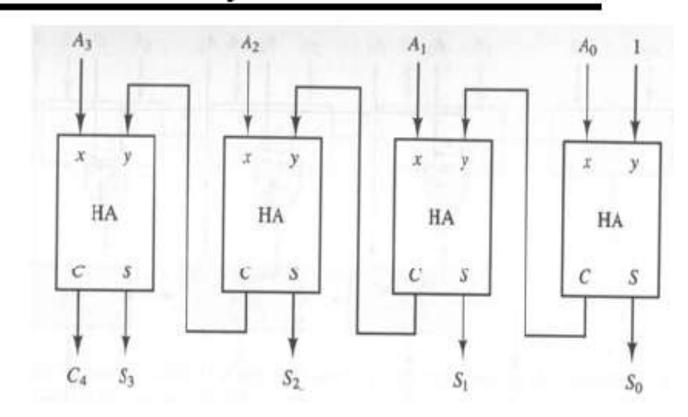

### **Binary Incrementer**

- Implemented by a binary counter

- Can use half-adders

- *n*-bit binary incrementer uses *n* half-adders

#### **4-Bit Binary Incrementer**

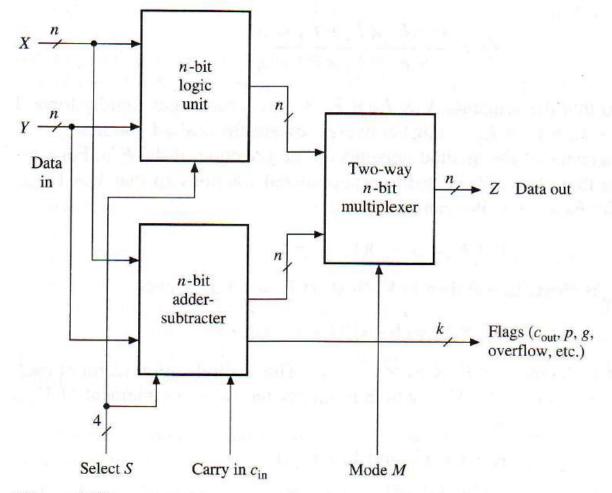

#### Arithmetic Circuit

- Arithmetic microoperations on slide #19 implemented in one circuit

- Base component is parallel adder

- Based on inputs to adder, can do different arithmetic operations

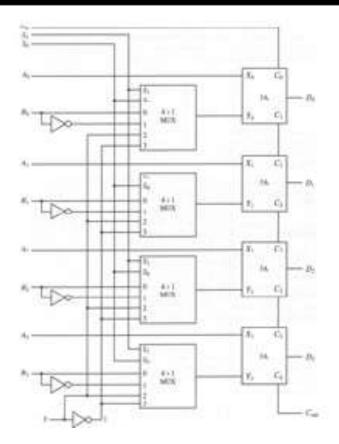

#### 4-Bit Arithmetic Circuit

- Two 4-bit inputs A and B

- One 4-bit output D

- Four inputs A go directly to X inputs of FA

- Input to 4x1 Multiplexers

- *B*, *B*′

- **■** 0, 1

- S<sub>0</sub>, S<sub>1</sub>

- Multiplexer output goes to Y input of FA

#### Arithmetic Circuit Function Table

| Select |       | In                | <u>Output</u> |                             |                   |

|--------|-------|-------------------|---------------|-----------------------------|-------------------|

| $S_1$  | $S_0$ | $C_{\mathrm{in}}$ | Y             | $D = A + Y + C_{\text{in}}$ | Microoperation    |

| 0      | 0     | 0                 | В             | D = A + B                   | Add               |

| 0      | 0     | 1                 | В             | D = A + B + 1               | Add w/carry       |

| 0      | 1     | 0                 | В             | $D = A + \overline{B}$      | Subtract w/borrow |

| 0      | 1     | 1                 | В             | $D = A + \overline{B} + 1$  | Subtract          |

| 1      | 0     | 0                 | 0             | D = A                       | Transfer A        |

| 1      | 0     | 1                 | 0             | D = A + 1                   | Increment A       |

| 1      | 1     | 0                 | 1             | D = A - 1                   | Decrement A       |

| 1      | 1     | 1                 | 1             | D = A                       | Transfer A        |

#### 4-Bit Arithmetic Circuit

### Logic Microoperations

- Binary operations on strings of bits stored in registers

- Each bit is dealt with separately

- Exclusive-OR example

- $\blacksquare P: R1 \leftarrow R1 \oplus R2$

- Contents of *R*1 0011

- Contents of *R*2 <u>0101</u>

- Contents of R1 after P = 1 0110

#### Special Symbols

- Logic microoperations

- OR v

- AND ∧

- Complement bar on top of register symbol

- Distinguish logic microoperation from Boolean function

$$P + Q: R1 \leftarrow R2 + R3, R4 \leftarrow R5 \lor R6$$

$\uparrow \qquad \qquad \uparrow OR microop$

$OR op between two control function binary variables$

### 2 Variable/16 Function Truth Table

| x | y | $F_0$ | $F_1$ | $F_2$ | $F_3$ | $F_4$ | $F_5$ | $F_{6}$ | $F_7$ | $F_{8}$ | $F_9$ | $F_{10}$ | $F_{11}$ | $F_{12}$ | $F_{13}$ | $F_{14}$ | $F_{15}$ |

|---|---|-------|-------|-------|-------|-------|-------|---------|-------|---------|-------|----------|----------|----------|----------|----------|----------|

| 0 | 0 | 0     | 0     | 0     | 0     | 0     | 0     | 0       | 0     | 1       | 1     | 1        | 1        | 1        | 1        | 1        | 1        |

| 0 | 1 | 0     | 0     | 0     | 0     | 1     | 1     | 1       | 1     | 0       | 0     | 0        | 0        | 1        | 1        | 1        | 1        |

| 1 | 0 | 0     | 0     | 1     | 1     | 0     | 0     | 1       | 1     | 0       | 0     | 1        | 1        | 0        | 0        | 1        | 1        |

| 1 | 1 | 0     | 1     | 0     | 1     | 0     | 1     | 0       | 1     | 0       | 1     | 0        | 1        | 0        | 1        | 0        | 1        |

### 16 Logic Microoperations – Part 1

| Boolean function   | Microoperation                       | Name         |

|--------------------|--------------------------------------|--------------|

| $F_0 = 0$          | $F \leftarrow 0$                     | Clear        |

| $F_1 = xy$         | $F \leftarrow A \wedge B$            | AND          |

| $F_2 = xy'$        | $F \leftarrow A \wedge \overline{B}$ |              |

| $F_3 = x$          | $F \leftarrow A$                     | Transfer A   |

| $F_4 = x'y$        | $F \leftarrow \overline{A} \wedge B$ |              |

| $F_5 = y$          | $F \leftarrow B$                     | Transfer B   |

| $F_6 = x \oplus y$ | $F \leftarrow A \oplus B$            | Exclusive-OR |

| $F_7 = x + y$      | $F \leftarrow A \lor B$              | OR           |

### 16 Logic Microoperations – Part 2

| Boolean function           | Microoperation                       | Name           |

|----------------------------|--------------------------------------|----------------|

| $F_8 = (x + y)'$           | $F \leftarrow \overline{A \lor B}$   | NOR            |

| $F_9 = (x \oplus y)'$      | $F \leftarrow \overline{A \oplus B}$ | Exclusive-NOR  |

| $F_{10} = y'$              | $F \leftarrow \overline{B}$          | Complement B   |

| $F_{11} = x + y'$          | $F \leftarrow A \lor \overline{B}$   |                |

| $F_{12} = x'$              | $F \leftarrow \overline{A}$          | Complement A   |

| $F_{13} = x' + y$          | $F \leftarrow \overline{A} \lor B$   |                |

| $F_{14} = (xy)'$           | $F \leftarrow \overline{A \land B}$  | NAND           |

| <i>F</i> <sub>15</sub> = 1 | $F \gets \text{all 1's}$             | Set to all 1's |

## Hardware Implementation

- Logic gates inserted for each bit or pair of bits in the registers to perform needed logic function

- Most computers use only four microoperations and derive the rest

- AND, OR, XOR, complement

### Examples

• Following slides are examples of logic microoperations that are used to manipulate individual bits of register A by the bits contained in another register, B

#### Selective Set

- Register A bits set to 1 where register B has a 1, otherwise A bits left unchanged

- 0011 A before x

- 0101 B (logic operand) y

- 0111 A after *F*<sub>7</sub>

- OR microoperation

#### Selective Complement

- Register A bits complemented where register B has a 1, otherwise A bits left unchanged

- 0011 A before x

- $\underline{0101}$  B (logic operand) y

- 0110 A after  $F_6$

- Exclusive-OR microoperation

#### Selective Clear

- Register A bits cleared to 0 where register B has a 1, otherwise A bits left unchanged

- 0011 A before x

- 0101 B (logic operand) y

- 0010 A after  $F_2$

- $A \leftarrow A \land \overline{B}$  logic microoperation

#### Mask

Register A bits cleared to 0 where register B has a 0, otherwise A bits left unchanged

$F_1$

- 0011 A before x

- 0101 B (logic operand) y

- 0001 A after

- AND microoperation

#### Insert

- Inserts a new value into a group of bits

- First mask the bits (AND)

- Next selective-set them with target bit string (OR)

- Insert 1110 into leftmost 4 bits of A

- 1001 0101 A before

- <u>0000 1111</u> B (mask)

- 0000 0101 A after masking

- <u>1110 0000</u> B (selective-set)

- 1110 0101 A after insert completes

#### Clear

- Compares bits in A and B and produces all zeros if the two registers have equal values

- Accomplished with exclusive-OR, then all bits are checked for being 0

#### Shift Microoperations

- First flip-flop gets binary data from serial input

- For shift left, "first" is rightmost flip-flop

- For shift right, "first" is leftmost flip-flop

- Serial input source determined by type of shift

- 0 for logical

- Other end for circular

- 0 fill on right and sign bit on left for arithmetic

- Overflow when sign bit changes

## Logical Shift Example

- Original value: 11010011

Value after shift right: 01101001

- Or, value after shift left: 10100110

#### **Circular Shift Example**

- Original value: 11010011

- Value after shift right: 11101001

- Or, value after shift left: 10100111

# Arithmetic Shift Example

- Original value: 11010011

- Value after shift right: 11101001

- Or, value after shift left: 10100110

- Second original value: 10011010

- Value after shift right: 11001101

- Or, value after shift left: 00110100 (overflow)

## **Overflow Flip-Flop**

- Bits in register:  $R_{n-1} R_{n-2} \dots R_1 R_0$

- V<sub>s</sub> detects arithmetic shift left overflow

= 1 indicates overflow condition

•

$$V_s = R_{n-1} \oplus R_{n-2}$$

# Shift Microoperations

| Symbolic designation                 | Description              |

|--------------------------------------|--------------------------|

| $R \leftarrow \operatorname{shl} R$  | Shift-left R             |

| $R \leftarrow \operatorname{shr} R$  | Shift-right R            |

| $R \leftarrow \operatorname{cil} R$  | Circular shift-left R    |

| $R \leftarrow \operatorname{cir} R$  | Circular shift-right R   |

| $R \leftarrow \operatorname{ashl} R$ | Arithmetic shift-left R  |

| $R \leftarrow \operatorname{ashr} R$ | Arithmetic shift-right R |

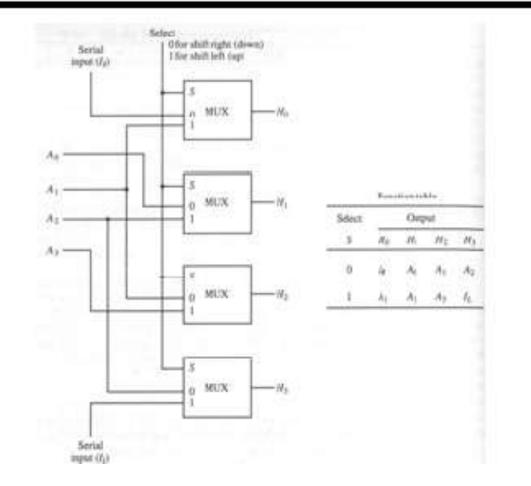

## Shift Hardware Implementation

- Register content is placed on bus

- Bus connected to combination circuit shifter

- Shifted value loaded back into same register

- All done in one clock pulse

#### 4-Bit Combinational Circuit Shifter

51

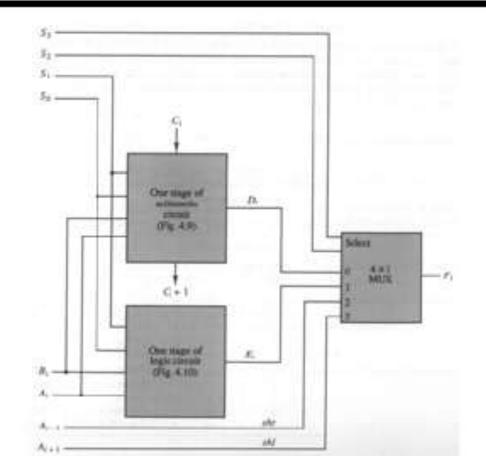

# Arithmetic Logic Unit (ALU)

- · One or more source registers provide input

- ALU performs operation

- Result transferred into destination register

- All done in one clock pulse

- Arithmetic, logic, and shift circuits can be combined into single ALU with common selection variables

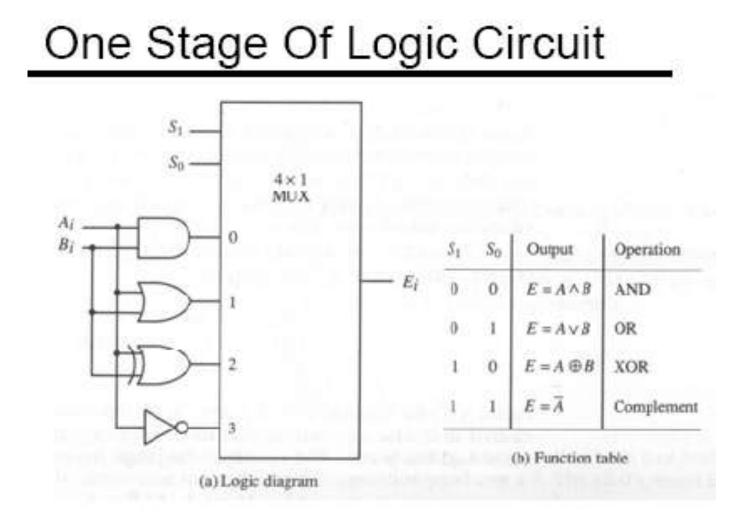

#### One Stage Of ALU

#### ALU Function Table

| Operation select                        |       |       |                       | peration select |                            |                      |

|-----------------------------------------|-------|-------|-----------------------|-----------------|----------------------------|----------------------|

| S,                                      | $S_2$ | $S_1$ | <i>S</i> <sub>0</sub> | Cin             | Operation                  | Function             |

| 0                                       | 0     | 0     | 0                     | 0               | F = A                      | Transfer A           |

| 0                                       | 0     | 0     | 0                     | 1               | F = A + 1                  | Increment A          |

|                                         | 0     | 0     | 1                     | 0               | F = A + B                  | Addition             |

| 0<br>0<br>0                             | 0     | 0     | 1                     | 1               | F = A + B + 1              | Add with carry       |

| 0                                       | 0     | 1     | 0                     | 0               | $F = A + \overline{B}$     | Subtract with borrow |

|                                         | 0     | 1     | 0                     | 1               | $F = A + \overline{B} + 1$ | Subtraction          |

| 000000000000000000000000000000000000000 | 0     | 1     | 1                     | 0               | F = A - 1                  | Decrement A          |

| 0                                       | 0     | 1     | 1                     | 1               | F - A                      | Transfer A           |

| 0                                       | 1     | 0     | 0                     | ×               | $F = A \wedge B$           | AND                  |

| 0                                       | 1     | 0     | 1                     | ×               | $F - A \vee B$             | OR                   |

| 0                                       | 1     | 1     | 0                     | ×               | $F = A \oplus B$           | XOR                  |

| 0                                       | 1     | 1     | 1                     | ~               | $F - \overline{A}$         | Complement A         |

| 1                                       | 0     | ×     | ×                     | ×               | $F = \operatorname{shr} A$ | Shift right A into F |

| 1                                       | 1     | ×     | ×                     | ×               | $F = \operatorname{shl} A$ | Shift left A into F  |

TABLE 4-8 Function Table for Arithmetic Logic Shift Unit

#### Elements of an Instruction

- Operation code (Op code)

- Do this

- Source Operand reference

To this

- Result Operand reference

- Put the answer here

- Next Instruction Reference

- When you have done that, do this...

# Where have all the Operands gone?

- Main memory (or virtual memory or cache)

- CPU register

- I/O device

# Instruction Representation

| OPCODE | OPERAND1 | OPERAND2 |

|--------|----------|----------|

|--------|----------|----------|

# Instruction Types

- Data processing

- Data storage (main memory)

- Data movement (I/O)

- Program flow control

# Number of Addresses (a)

- 3 addresses

- Operand 1, Operand 2, Result

- a = b + c;

- May be a forth next instruction (usually implicit)

- Not common

- Needs very long words to hold everything

# Number of Addresses (b)

- 2 addresses

- One address doubles as operand and result

- -a = a + b

- Reduces length of instruction

- Requires some extra work

- Temporary storage to hold some results

# Number of Addresses (c)

- 1 address

- Implicit second address

- Usually a register (accumulator)

- Common on early machines

# Number of Addresses (d)

- 0 (zero) addresses

- All addresses implicit

- Uses a stack

- e.g. push a

- push b

- add

- рорс

-c = a + b

# How Many Addresses

- More addresses

- More complex (powerful?) instructions

- More registers

- Inter-register operations are quicker

- Fewer instructions per program

- Fewer addresses

- Less complex (powerful?) instructions

- More instructions per program

- Faster fetch/execution of instructions

# Design Decisions (1)

- Operation repertoire

- How many ops?

- What can they do?

- How complex are they?

- Data types

- Instruction formats

- Length of op code field

- Number of addresses

# Design Decisions (2)

- Registers

- Number of CPU registers available

- Which operations can be performed on which registers?

- Addressing modes (later...)

• RISC v CISC

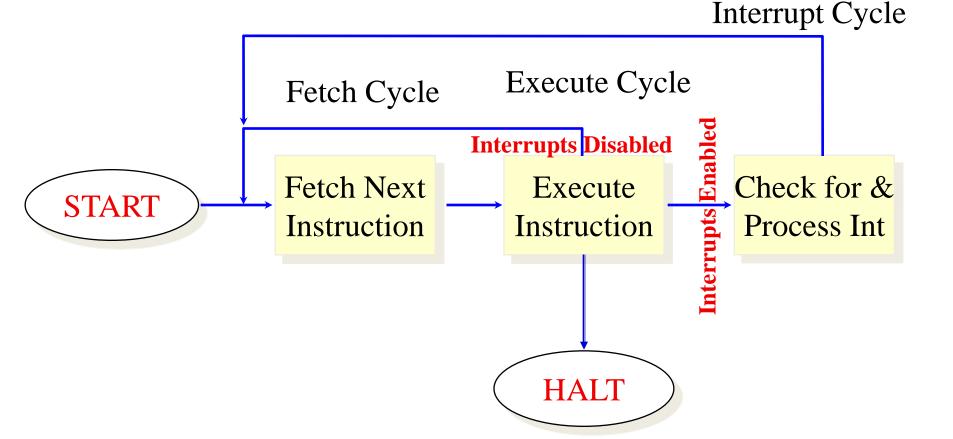

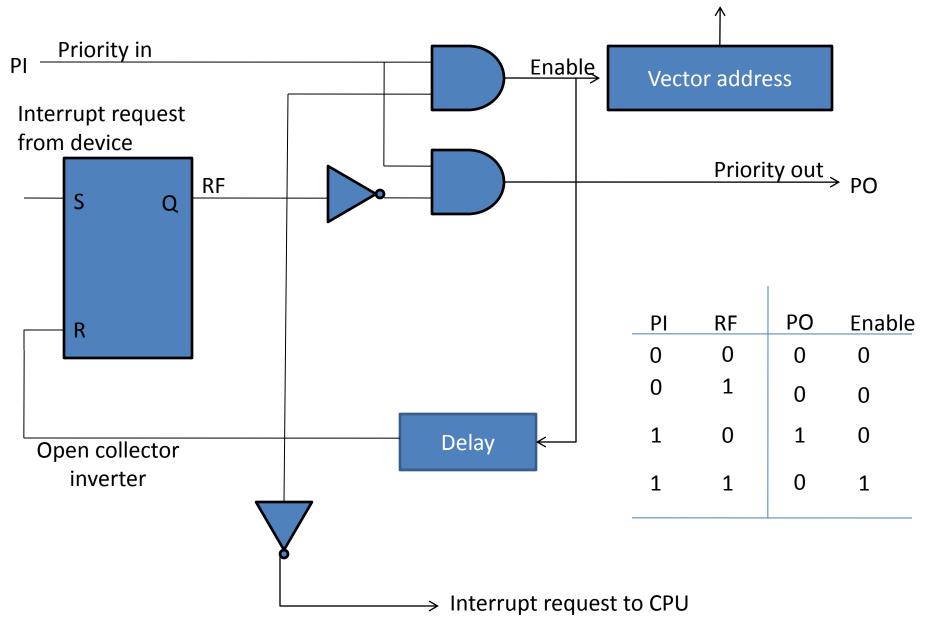

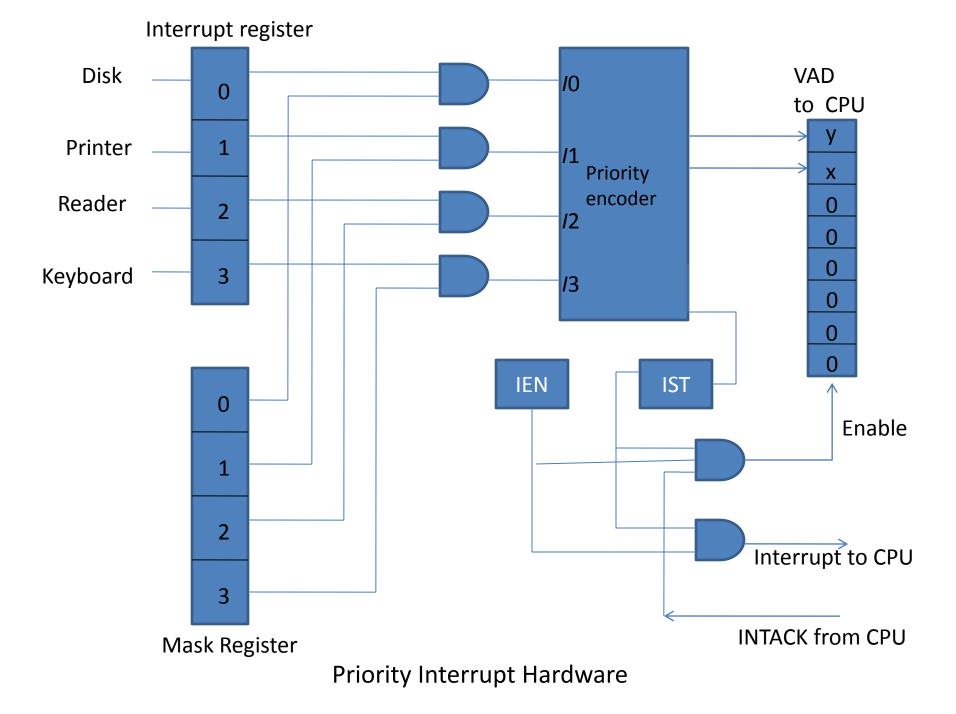

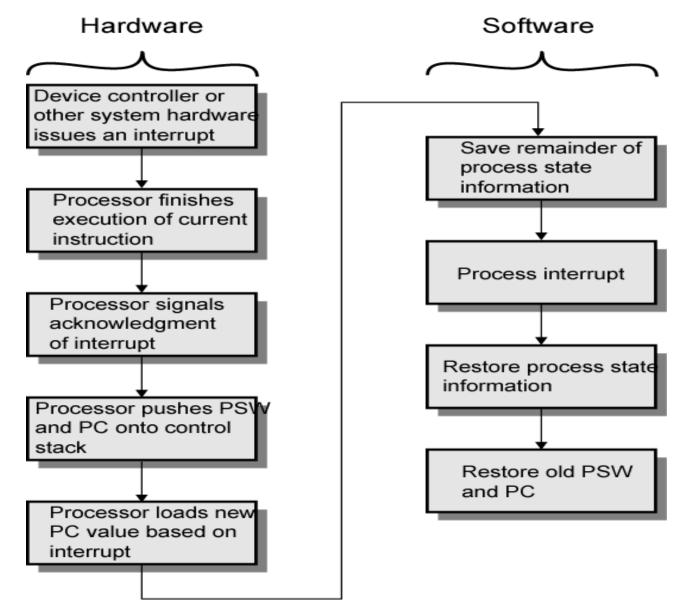

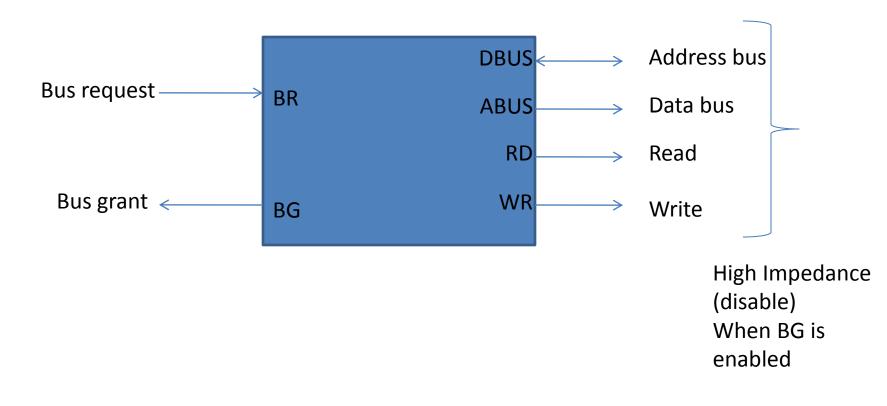

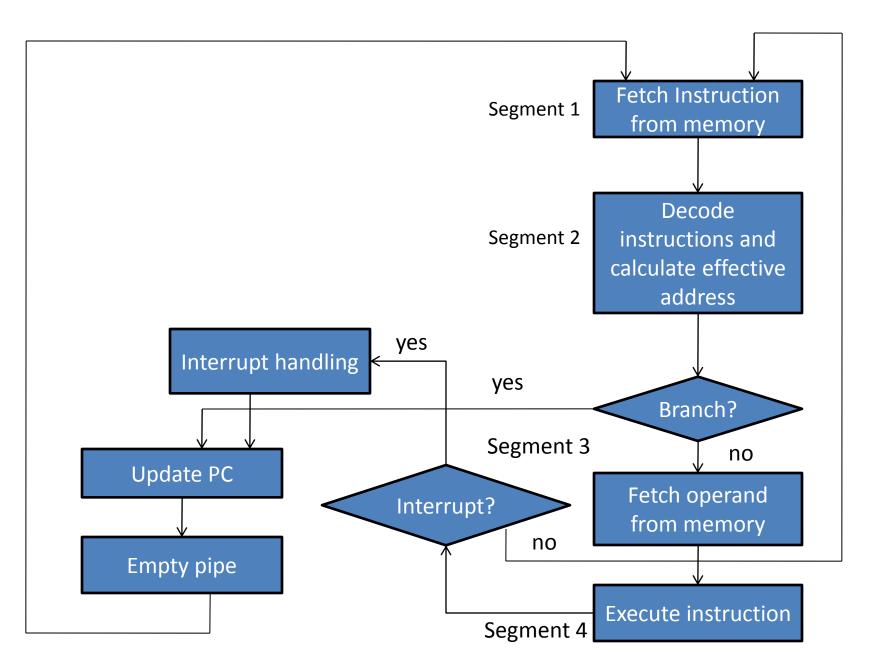

Instruction cycle with interrupt

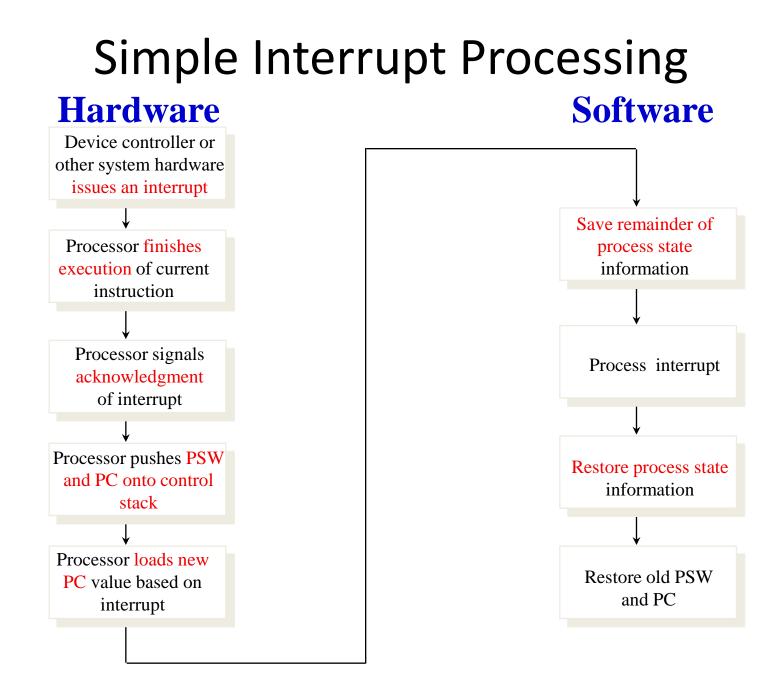

# Interrupts - In Summary

- An interruption of normal processing

- Improves processing efficiency

- Allows the processor to execute other instructions while an I/O operation is in progress

- A suspension of a process caused by an event external to that process and performed in such a way that the process can be resumed

# **Classes of Interrupts**

#### • Program

- arithmetic overflow

- division by zero

- execute illegal instruction

- reference outside user's memory space

- Timer

- 1/0

- Hardware failure

# **Common Functions of Interrupts**

- Interrupts transfer control to the interrupt service routine generally, through the *interrupt vector*

- Interrupt architecture must save the address of the interrupted instruction.

- interrupts are *disabled* while another interrupt is being processed to prevent a *lost interrupt*.

- A *trap* is a software-generated interrupt caused either by an error or a user request.

- An operating system is interrupt driven.

- Interrupt Handling

The operating system preserves the state of the CPU by storing registers and the program counter.

- Determines which type of interrupt has occurred:

- polling

- vectored interrupt system

- Separate segments of code determine what action should be taken for each type of interrupt

# Instruction Cycle with Interrupts

# Interrupt Cycle

- Processor checks for interrupts

- If no interrupts fetch the next instruction for the current program

- If an interrupt is pending, suspend execution of the current program, and execute the interrupt handler

# Interrupt Service Routine (aka handler)

- A program that determines nature of the interrupt and performs whatever actions are needed

- Control is transferred to this program

- Generally part of the operating system

# What about Multiple Interrupts

- Simple Approach disable interrupts

- Use Priorities to differentiate between interrupt classes

# Multiple Interrupts Sequential Order

- Disable interrupts so processor can complete task

- Interrupts remain pending until the processor enables interrupts

- After interrupt handler routine completes, the processor checks for additional interrupts

# **Multiple Interrupts Priorities**

- Higher priority interrupts cause lowerpriority interrupts to wait

- Causes a lower-priority interrupt handler to be interrupted

- Example when input arrives from communication line, it needs to be absorbed quickly to make room for more input

Unit – 03 CPU & Control Unit

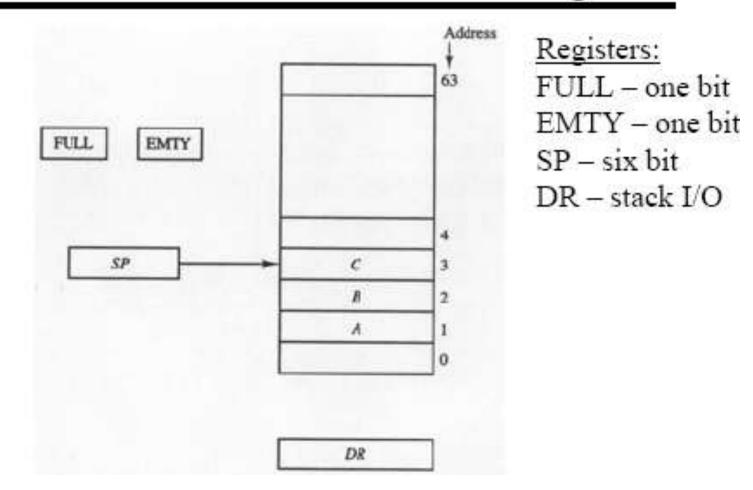

# Stack

- Last-in first-out (LIFO) list

- Stack pointer (SP)

- Always points to top item in stack

- Register that holds stack address

- Operations

- Push put new item in top of stack

- Pop remove item from top of stack

#### 64-Word Stack Block Diagram

## Stack Initialization

- SP cleared to 0

- EMTY set to 1

- FULL cleared to 0

#### Push

- $SP \leftarrow SP + 1$

- $M[SP] \leftarrow DR$

- If (SP = 0) then  $(FULL \leftarrow 1)$

- $EMTY \leftarrow 0$

### Pop

- $DR \leftarrow M[SP]$

- $SP \leftarrow SP 1$

- If (SP = 0) then  $(EMTY \leftarrow 1)$

- $FULL \leftarrow 0$

### Memory Layout Example

In this example, PUSH decrements SP POP increments SP

# Arithmetic Expression Notations

- A + B Infix

- +AB Prefix or Polish

- AB+ Postfix or reverse Polish

# **RPN Processing Algorithm**

- Scan expression from left to right

- When you find an operator

- Apply it to the two previous operands

- Replace operator and two operands just used with result

- Resume left to right scan, repeat above steps until no more operators

- Works well with a stack

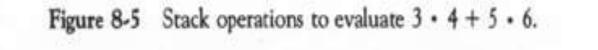

# **RPN** Example

- A \* B + C \* D becomes A B \* C D \* +

- Stepwise evaluation

■ A B \* C D \* +

- (A \* B) C D \* + where (A \* B) is a single value

- (A \* B) (C \* D) + where (C \* D) is a single value

- ((A \* B) + (C \* D)) which is a single value

# Another RPN Example

- 8 \* 2 + 5 \* 3 becomes 8 2 \* 5 3 \* +

- Stepwise evaluation

- 8 2 \* 5 3 \* +

- 16 5 3 \* +

- 16 15 +

- **3**1

# Another Infix to RP

- Infix (A + B) \* (C \* (D + E) + F)

- RP AB + DE + C \* F + \*

- RPN doesn't need or use parentheses

## Stack Operations

- Infix: 3 \* 4 + 5 \* 6

- RP: 3 4 \* 5 6 \* +

# **Instruction Formats**

The format of an instruction is usually depicted in a rectangular box symbolizing the bits of the instruction as they appear in memory words or in a control register. The bits of the instructions are divided into groups called fields. The most common fields found in instruction format are:-

- 1. An Operation code field that specifies the operation to be performed.

- 2. An address field that designates a memory address or a processor register.

- 3. A mode field that specifies the way the operand or the effective address is determined.

Computer may have instructions of several different length containing varying number of addresses. The no. of address field in the instruction format of a computer depends on the internal organization of its registers.

# Types of CPU Organizations

- Single accumulator

- General register

- Stack

- Some CPUs combine features from more than one organization type

# Single Accumulator

• ADD X •  $AC \leftarrow AC + M[X]$

### General Register

- ADD R1, R2, R3  $\blacksquare R1 \leftarrow R2 + R3$

- ADD R1, R2

- $\blacksquare R1 \leftarrow R1 + R2$

- MOV R1, R2

- $\blacksquare R1 \leftarrow R2$

- ADD R1, X •  $R1 \leftarrow R1 + M[X]$

#### Stack

- PUSH X

- ADD

- Zero address

- Pop two numbers off stack

- Add them

- Push result back on stack

### Three Address Instructions

- X = (A + B) \* (C + D)

- ADD R1, A, B  $R1 \leftarrow M[A] + M[B]$ ADD R2, C, D  $R2 \leftarrow M[C] + M[D]$ MUL X, R1, R2  $M[X] \leftarrow R1 * R2$

### Two Address Instructions

- X = (A + B) \* (C + D)

- MOV R1, A

- ADD R1, B

- MOV R2, C

- ADD R2, D MUL R1, R2

- MOV X, R1

### **One Address Instructions**

- X = (A + B) \* (C + D)

- LOAD A

ADD B

STORE T

LOAD C

ADD D

MUL T

- STORE X

### Zero Address Instructions

- X = (A + B) \* (C + D)

- PUSH A

PUSH B

ADD

PUSH C

PUSH D

ADD

ADD

MUL

- POP X

# Addressing Modes

# Addressing Mode Techniques

- Useful for

- Reducing the number of bits in the address field of the instruction

- Writing programming loops, indexing data, using memory pointers, relocating programs in memory

| Figure 8-6 | Instruction format with mode field. |         |

|------------|-------------------------------------|---------|

| Opcode     | Mode                                | Address |

# Addressing Modes

- Implied operands specified implicitly

- E.g., "complement accumulator"

- Immediate operand value in address field

- Register operand in register specified in register field

- Register Indirect register contains indirect address

- Autoincrement or Autodecrement like register indirect, except register value is incremented or decremented after it is used

# More Addressing Modes

- Direct Address effective address is in address part of the instruction

- Indirect Address effective address is stored in memory location specified in address part of the instruction

- Relative Address program counter added to address part of the instruction

- Indexed Addressing value of index register added to address part of the instruction to yield effective address

- Base Register Addressing similar to Indexed

### Addressing Modes Example

|   | <i>PC</i> = 200  |  |

|---|------------------|--|

|   | <i>R</i> 1 = 400 |  |

|   | $\chi g = 100$   |  |

| Г | AC               |  |

| ddress | Memory           |      |  |

|--------|------------------|------|--|

| 200    | Load to AC       | Mode |  |

| 201    | Address = 500    |      |  |

| 202    | Next instruction |      |  |

|        |                  |      |  |

| 399    | 450              |      |  |

| 400    | 700              |      |  |

| 500    | 800              |      |  |

| 600    | 900              |      |  |

| 702    | 325              |      |  |

| 800    | 300              |      |  |

Direct Immediate Indirect Relative Indexed Register Register Indirect Autoincrement Autodecrement

35

# Numerical Example

| Addressing<br>Mode | Effective<br>Address | Content<br>of AC |

|--------------------|----------------------|------------------|

| Direct address     | 500                  | 800              |

| Immediate operand  | 201                  | 500              |

| Indirect address   | 800                  | 300              |

| Relative address   | 702                  | 325              |

| Indexed address    | 600                  | 900              |

| Register           |                      | 400              |

| Register indirect  | 400                  | 700              |

| Autoincrement      | 400                  | 700              |

| Autodecrement      | 399                  | 450              |

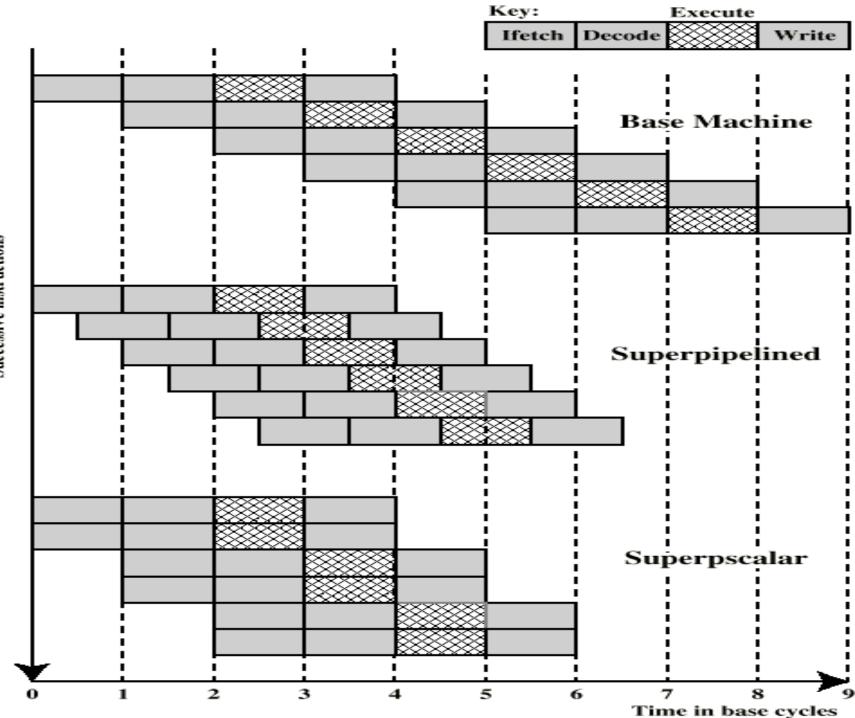

# RISC vs CISC

#### RISC

- Emphasis on hardware

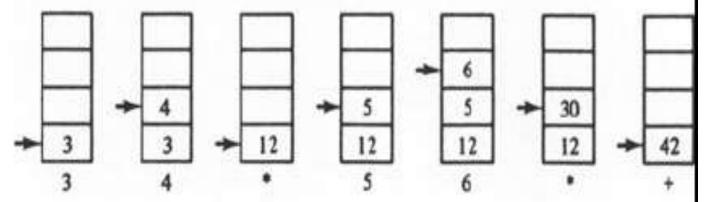

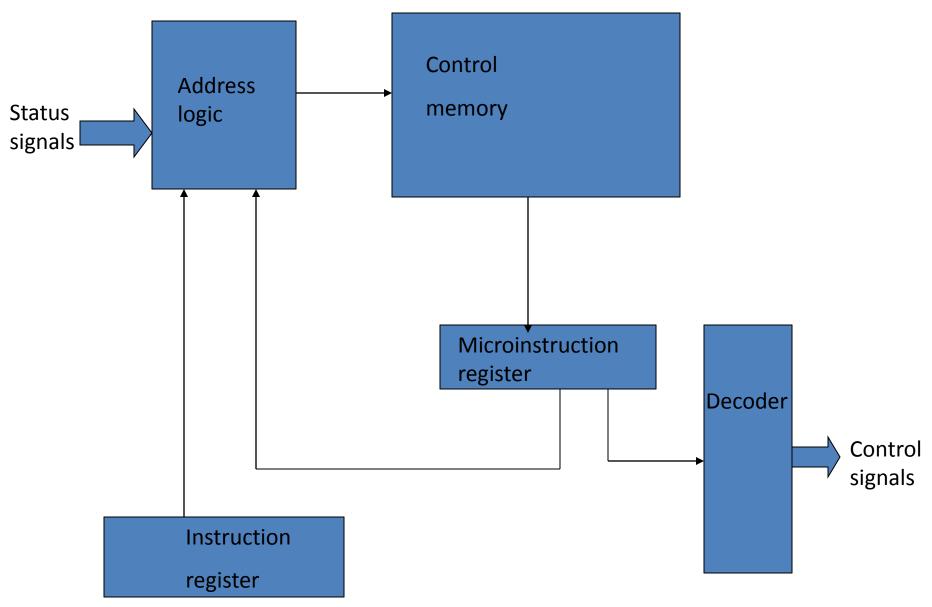

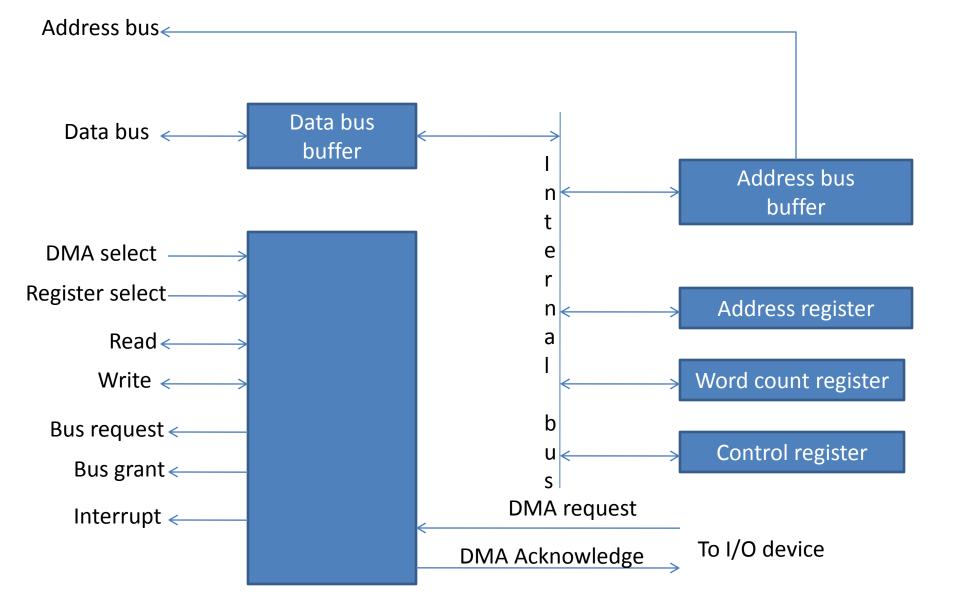

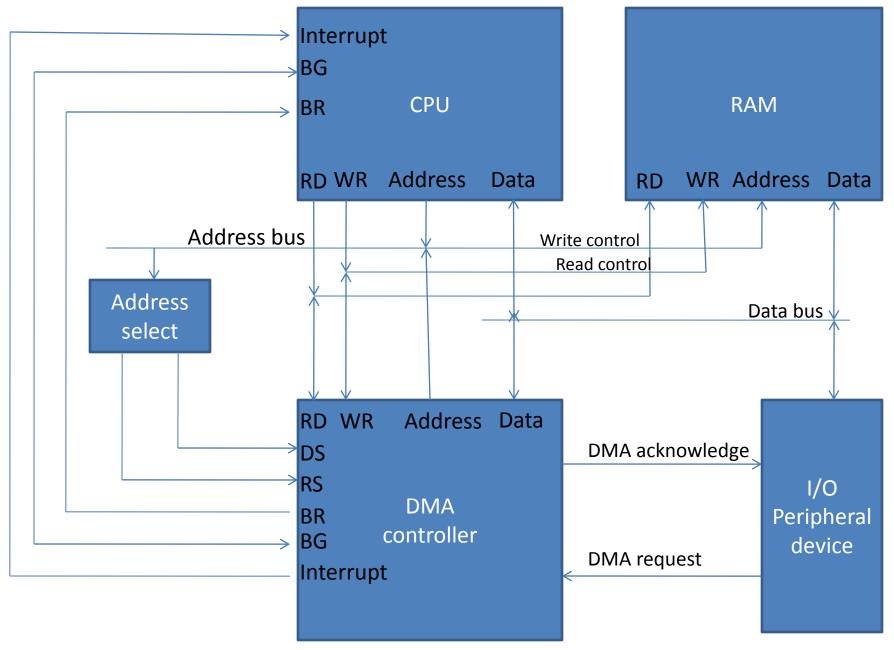

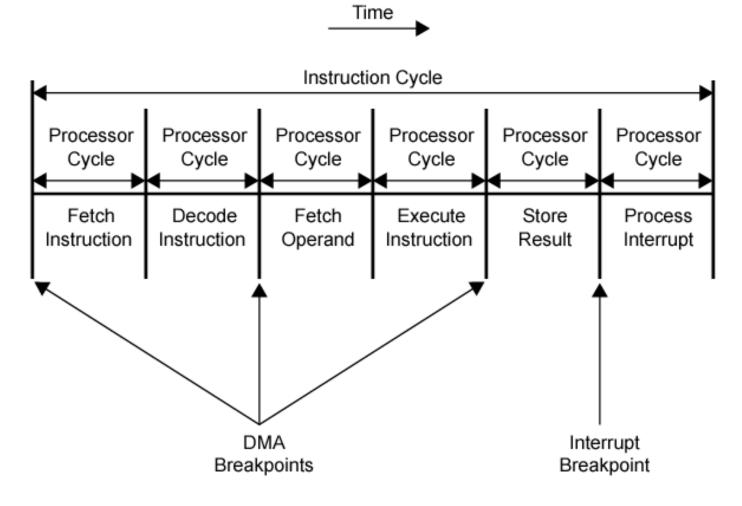

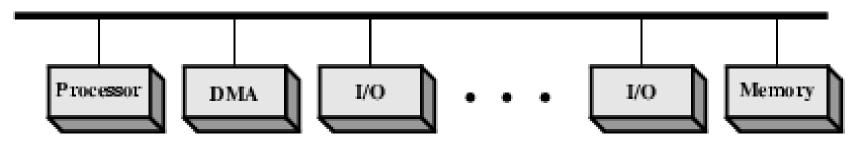

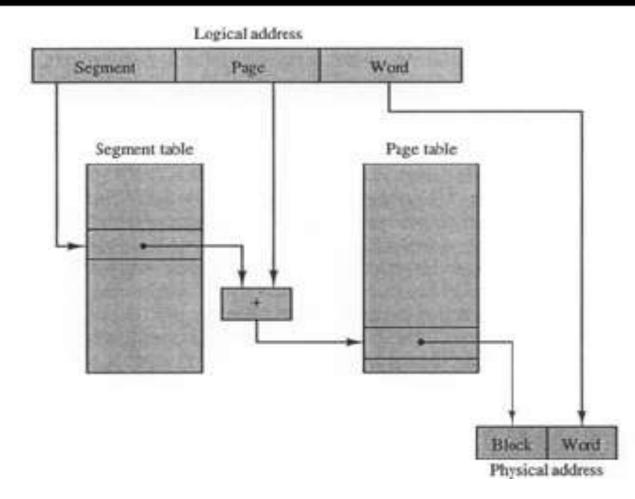

- Includes multi-clock